US 20070085781 A1

(19) United States

(12) Patent Application Publication (10) Pub. No.: US 2007/0085781 A1

Chung et al.

(43) Pub. Date: Apr. 19, 2007

(54) DATA DRIVING CIRCUITS AND ORGANIC

LIGHT EMITTING DISPLAYS USING THE

SAME

Publication Classification

(51) Int. Cl.

*G09G 3/30* (2006.01)

(52) U.S. Cl. ..... 345/76

(76) Inventors: Bo Yong Chung, Seoul (KR); Do Hyung Ryu, Suwon-si (KR); Oh Kyong Kwon, Seoul (KR)

(57) ABSTRACT

Correspondence Address:

LEE & MORSE, P.C.

3141 FAIRVIEW PARK DRIVE

SUITE 500

FALLS CHURCH, VA 22042 (US)

(21) Appl. No.: 11/491,910

(22) Filed: Jul. 25, 2006

(30) Foreign Application Priority Data

Aug. 1, 2005 (KR) ..... 2005-70439

A data driving circuit for driving pixels of a display to display images with uniform brightness may include a gamma voltage unit that generates gray scale voltages, a digital-analog converter that selects, as a data signal, one of the gray scale voltages using first data, a decoder that generates second data using the first data, a latch for storing the first data and the second data, a current sink that receives a predetermined current from the pixel during a first partial period of a complete period for driving the pixel based on the selected gray scale voltage, a voltage controller that controls a voltage value of the data signal using the second data and a compensation voltage generated based on the predetermined current, and a switching unit that supplies the data signal to the pixel during any partial period of the complete period elapsing after the first partial period.

FIG. 1

(RELATED ART)

FIG. 2

FIG. 3

140nm

FIG. 4

FIG. 5

140nm'

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

**DATA DRIVING CIRCUITS AND ORGANIC LIGHT EMITTING DISPLAYS USING THE SAME****BACKGROUND OF THE INVENTION****[0001] 1. Field of the Invention**

**[0002]** The present invention relates to data driving circuits, light emitting displays employing such data driving circuits and methods of driving the light emitting display. More particularly, the invention relates to a data driving circuit capable of displaying images with uniform brightness, a light emitting display using such a data driving circuit and a method of driving the light emitting display to display images with uniform brightness.

**[0003] 2. Description of Related Art**

**[0004]** Flat panel displays (FPDs), which are generally lighter and more compact than cathode ray tubes (CRTs), are being developed. FPDs include liquid crystal displays (LCDs), field emission displays (FEDs), plasma display panels (PDPs) and light emitting displays.

**[0005]** Light emitting displays may display images using organic light emitting diodes (OLEDs) that generate light when electrons and holes re-combine. Light emitting displays generally have fast response times and consume relatively low amounts of power.

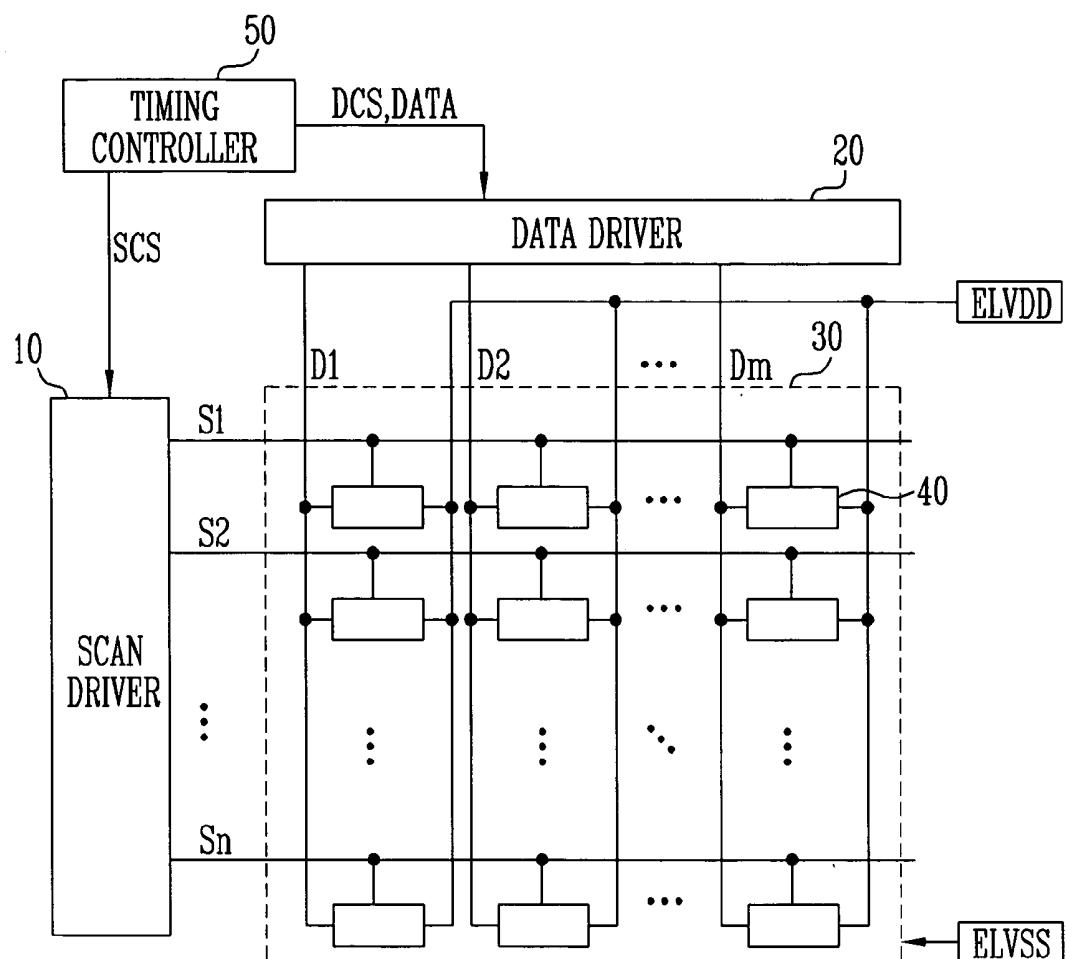

**[0006]** FIG. 1 illustrates a schematic of the structure of a known light emitting display.

**[0007]** As shown in FIG. 1, the light emitting display may include a pixel unit 30, a scan driver 10, a data driver 20 and a timing controller 50. The pixel unit 30 may include a plurality of pixels 40 connected to scan lines S1 to Sn and data lines D1 to Dm. The scan driver 10 may drive the scan lines S1 to Sn. The data driver 20 may drive the data lines D1 to Dm. The timing controller 50 may control the scan driver 10 and the data driver 20.

**[0008]** The timing controller 50 may generate data driving control signals DCS and scan driving control signals SCS based on externally supplied synchronizing signals (not shown). The data driving control signals DCS may be supplied to the data driver 20 and the scan driving control signals SCS may be supplied to the scan driver 10. The timing controller 50 may supply data DATA to the data driver 20 in accordance with externally supplied data (not shown).

**[0009]** The scan driver 10 may receive the scan driving control signals SCS from the timing controller 50. The scan driver 10 may generate scan signals (not shown) based on the received scan driving control signals SCS. The generated scan signals may be sequentially supplied to the pixel unit 30 via the scan lines S1 to Sn.

**[0010]** The data driver 20 may receive the data driving control signals DCS from the timing controller 50. The data driver 20 may generate data signals (not shown) based on the received data DATA and data driving control signals DCS. Corresponding ones of the generated data signals may be supplied to the data lines D1 to Dm in synchronization with respective ones of the scan signals being supplied to the scan lines S1 to Sn.

**[0011]** The pixel unit 30 may be connected to a first power source ELVDD for supplying a first voltage VDD and a

second power source ELVSS for supplying a second voltage VSS to the pixels 40. The pixels 40, together with the first voltage VDD signal and the second voltage VSS signal, may control the currents that flow through respective OLEDs in accordance with the corresponding data signals. The pixels 40 may thereby generate light based on the first voltage VDD signal, the second voltage VSS signal and the data signals.

**[0012]** In known light emitting displays, each of the pixels 40 may include a pixel circuit including at least one transistor for selectively supplying the respective data signal and the respective scan signal for selectively turning on and turning off the respective pixel 40 of the light emitting display.

**[0013]** Each pixel 40 of a light emitting display is to generate light of predetermined brightness in response to various values of the respective data signals. For example, when the same data signal is applied to all the pixels 40 of the display, it is generally desired for all the pixels 40 of the display to generate the same brightness. The brightness generated by each pixel 40 is not, however, only dependent on the data signal, but is also dependent on characteristics of each pixel 40, e.g., threshold voltage of each transistor of the pixel circuit.

**[0014]** Generally, there are variations in threshold voltage and/or electron mobility from transistor to transistor such that different transistors have different threshold voltages and electron mobilities. The characteristics of transistors may also change over time and/or usage. For example, the threshold voltage and electron mobility of a transistor may be dependent on the on/off history of the transistor.

**[0015]** Therefore, in a light emitting display, the brightness generated by each pixel in response to respective data signals depends on the characteristics of the transistor(s) that may be included in the respective pixel circuit. Such variations in threshold voltage and electron mobility may prevent and/or hinder the uniformity of images being displayed. Thus, such variations in threshold voltage and electron mobility may also prevent the display of an image with a desired brightness.

**[0016]** Although it may be possible to at least partially compensate for differences between threshold voltages of the transistors included in the pixels by controlling the structure of the pixel circuits of the pixels 40, circuits and methods capable of compensating for the variations in electron mobility are still needed. Light emitting devices, e.g., OLEDs, that are capable of displaying images with uniform brightness irrespective of variations in electron mobility are also desired.

**SUMMARY OF THE INVENTION**

**[0017]** The present invention is therefore directed to a data driving circuit and a light emitting display using the same, which substantially overcome one or more of the problems due to the limitations and disadvantages of the related art.

**[0018]** It is therefore a feature of an embodiment of the present invention to provide a data driving circuit capable of driving pixels of a light emitting display to display images with uniform brightness, a light emitting display using the same, and a method of driving the light emitting display.

[0019] At least one of the above and other features and advantages of the present invention may be realized by providing a data driving circuit including a decoder for generating second data having p bits using externally supplied first data having k bits, a latch for storing the first data and the second data, a gamma voltage unit for generating a plurality of gray scale voltages, a digital-to-analog converter for selecting one gray scale voltage among the plurality of gray scale voltages as a data signal based on the first data, a current sink unit receiving a predetermined current from a pixel during a first partial period of a complete period for driving the pixel based on the selected gray scale voltage, a voltage controller for controlling a voltage value of the data signal based on a compensation voltage generated based on the predetermined current and the second data, and a switching unit for supplying the controlled data signal to the pixel during a second partial period of the one complete period, the second partial period being different from the first partial period and the second partial period elapsing after the first partial period.

[0020] The decoder may convert the first data into a binary weighted value to generate the second data. The data driving circuit may further include a first transistor disposed between the digital-analog converter and the switching unit, the digital-analog converter being turned on during a predetermined time of the first partial period to transfer the data signal, with the controlled voltage value, to the switching unit, and a first buffer connected between the first transistor and the switching unit. The gamma voltage unit may include a plurality of distribution resistors for generating the gray scale voltages and distributing a reference supply voltage and a first supply voltage, and a second buffer for supplying the first supply voltage to the voltage controller.

[0021] The voltage controller may include p capacitors, each of the capacitors having a first terminal connected to an electrical path between the first transistor and the first buffer, second transistors respectively connected between a second terminal of each of the p capacitors and the second buffer, third transistors connected respectively between the second terminals of the p capacitors and the current sink unit and having a conduction type different from a conduction type of the second transistors, fourth transistors connected between the second transistors and a predetermined voltage source and having a same conduction type as the conduction type of the second transistors, and fifth transistors having a same conduction type as the conduction type of the third transistors, the fifth transistors for supplying the second data to the second transistors.

[0022] The fourth transistors may be turned on during the first period so that the second transistors may be turned on to supply a voltage of the predetermined voltage source to gate electrodes of the second transistors. The predetermined voltage source may be a ground voltage source. The third transistors may be selectively turned on during the first partial period so that the second terminals of the capacitors are set to have the voltage of the predetermined voltage source. The fifth transistors may consist of p transistors, corresponding to the number of bits of the second data, and the fifth transistors may respectively supply different bits of the p bits of second data to the second transistors.

[0023] Each of the third transistors that receives a bit having a value of 1 may be turned on to supply the respective

compensation voltage to the second terminals of the respective p capacitors. Capacitances of the p capacitors may be set to binary weighted values. The current sink unit may include a current source providing the predetermined current, a first transistor provided between a data line connected to the pixel and the voltage controller, the first transistor being turned on during the first partial period, a second transistor provided between the data line and the current source, the second transistor being turned on in the first partial period, a capacitor for charging the compensation voltage, and a buffer provided between the first transistor and the voltage controller to selectively transmit the compensation voltage to the voltage controller.

[0024] The predetermined current may be equal to a current value of a minimum current flowing through the pixel when the pixel emits light with maximum brightness, and maximum brightness may correspond to a brightness of the pixel when a highest one of the plurality of reset gray scale voltages is applied to the pixel. The switching unit may include at least one transistor that is turned on during the second partial period. The switching unit may include two transistors which are connected so as to form a transmission gate. The data driving circuit may further include a shift register unit including at least one shift register to sequentially generate sampling pulses and to supply the sampling pulses to the latch unit.

[0025] The latch unit may include a sampling latch unit including at least one sampling latch for receiving the first and second data in response to the sampling pulses, a holding latch unit including at least one holding latch for receiving the first and second data stored in the sampling latch unit to supply the first data stored therein to the digital-to-analog converter and to supply the second data to the voltage controller.

[0026] Each of the sampling latches and the holding latches may have a magnitude of k+p bits. The data driving circuit may further include a level shifter unit for increasing voltage levels of the first data and the second data stored in the holding latch to respectively supply the adjusted voltage levels of the stored first data and the stored second data to the digital-to-analog converter and the voltage controller.

[0027] At least one of the above and other features and advantages of the present invention may be realized by providing a light emitting display including a pixel unit including a plurality of pixels connected to n scan lines, a plurality of data lines, and a plurality of emission control lines, a scan driver respectively and sequentially supplying, during each scan cycle, n scan signals to the n scan lines, and for sequentially supplying emission control signals to the plurality of emission control lines, and a data driver having at least one data driving circuit for respectively supplying data signals to the data lines, wherein the data driving circuit include a decoder for generating second data having p bits using externally supplied first data having k bits, a latch for storing the first data and the second data, a gamma voltage unit for generating a plurality of gray scale voltages, a digital-to-analog converter for selecting one gray scale voltage among the plurality of gray scale voltages as a data signal based on the first data, a current sink unit receiving a predetermined current from a pixel during a first partial period of a complete period for driving the pixel based on the selected gray scale voltage, a voltage controller for

controlling a voltage value of the data signal based on a compensation voltage generated based on the predetermined current and the second data, and a switching unit for supplying the controlled data signal to the pixel during a second partial period of the one complete period, the second partial period being different from the first partial period and the second partial period elapsing after the first partial period.

[0028] Each of the pixels may be connected to two of the n scan lines, and during each of the scan cycles, a first of the two scan lines receiving a respective one of the n scan signals before a second of the two scan lines receives a respective one of the n scan signals, and each of the pixels may include a first power source, a light emitter receiving current from the first power source, first and second transistors each having a first electrode connected to the respective one of the data lines associated with the pixel, the first and second transistors being turned on when the first of the two scan signals is supplied, a third transistor having a first electrode connected to a reference power source and a second electrode connected to a second electrode of the first transistor, the third transistor being turned on when the first of the two scans signal is supplied, a fourth transistor controlling an amount of current supplied to the light emitter, a first terminal of the fourth transistor being connected to the first power source, and a fifth transistor having a first electrode connected to a gate electrode of the fourth transistor and a second electrode connected to a second electrode of the fourth transistor, the fifth transistor being turned on when the first of the two scan signals is supplied such that the fourth transistor operates as a diode.

[0029] Each of the pixels may include a first capacitor having a first electrode connected to one of a second electrode of the first transistor or the gate electrode of the fourth transistor and a second electrode connected to the first power source and a second capacitor having a first electrode connected to the second electrode of the first transistor and a second electrode connected to the gate electrode of the fourth transistor. Each of the pixels may further include a sixth transistor having a first terminal connected to the second electrode of the fourth transistor and a second terminal connected to the light emitter, the sixth transistor being turned off when the respective emission control signal is supplied, wherein the current sink may receive the predetermined current from the pixel during a first partial period of one complete period for driving the pixel, the first partial period occurring before a second partial period of the complete period for driving the pixel, and the sixth transistor may be turned on during the second partial period of the complete period for driving the pixel.

[0030] At least one of the above and other features and advantages of the present invention may be separately realized by providing a data driving circuit including a converting unit for generating second data having p bits using externally supplied first data having k bits, a latching unit for storing the first data and the second data, the latch having a magnitude of k+p bits, a selecting unit for selecting one gray scale voltage among the plurality of gray scale voltages as a data signal based on the first data, a current receiving unit for receiving a predetermined current from a pixel during a first partial period of a complete period for driving the pixel based on the selected gray scale voltage, a controlling unit for controlling a voltage value of the data

signal based on a compensation voltage generated based on the predetermined current and the second data, and after controlling the voltage value of the data signal, supplying the controlled data signal to the pixel during a second partial period of the one complete period, the second partial period being different from the first partial period and the second partial period elapsing after the first partial period.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0031] These and other features and advantages of the invention will become apparent to those of ordinary skill in the art by describing in detail exemplary embodiments thereof with reference to the attached drawings in which:

[0032] FIG. 1 illustrates a schematic diagram of a known light emitting display;

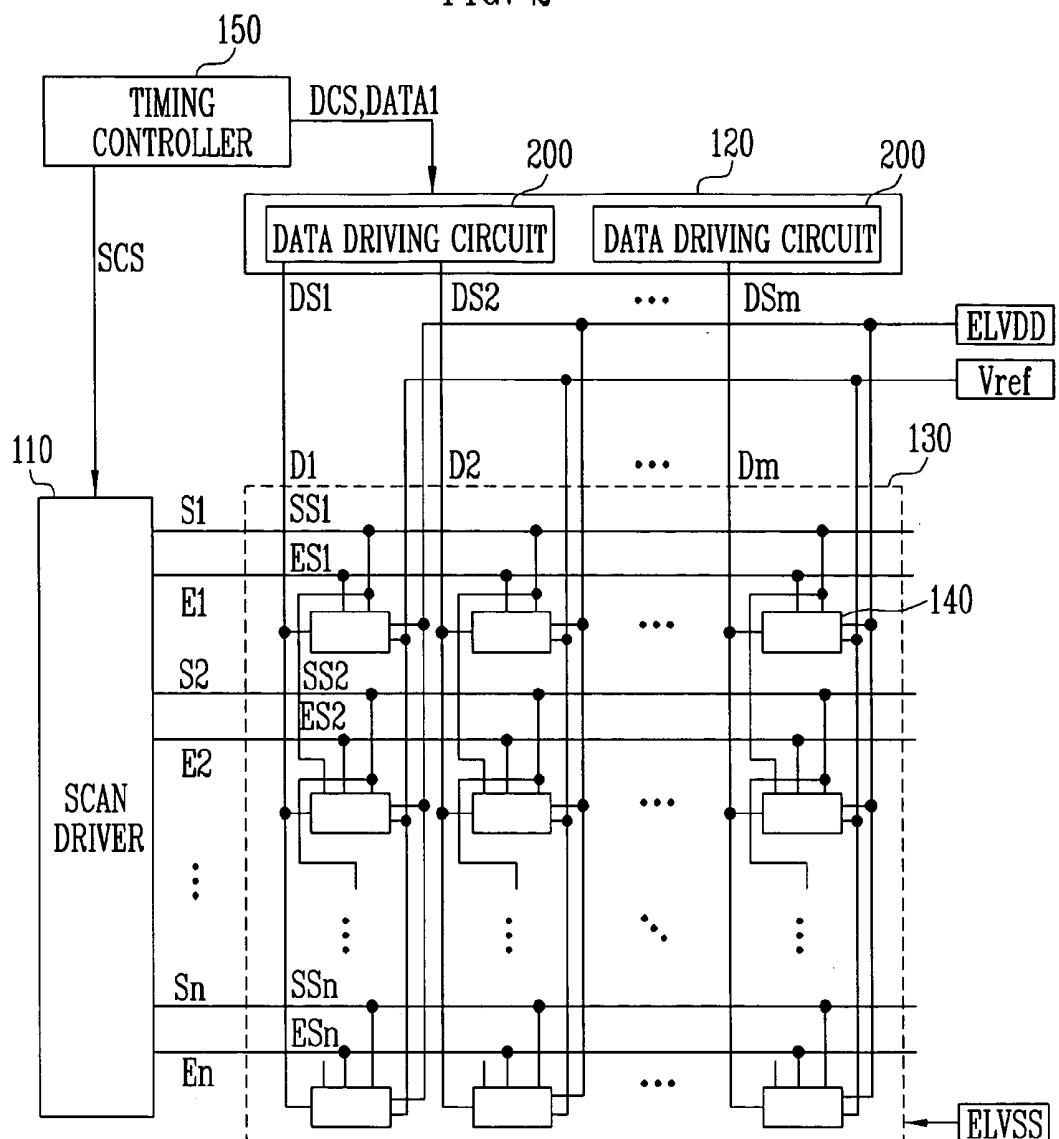

[0033] FIG. 2 illustrates a schematic diagram of a light emitting display according to an embodiment of the present invention;

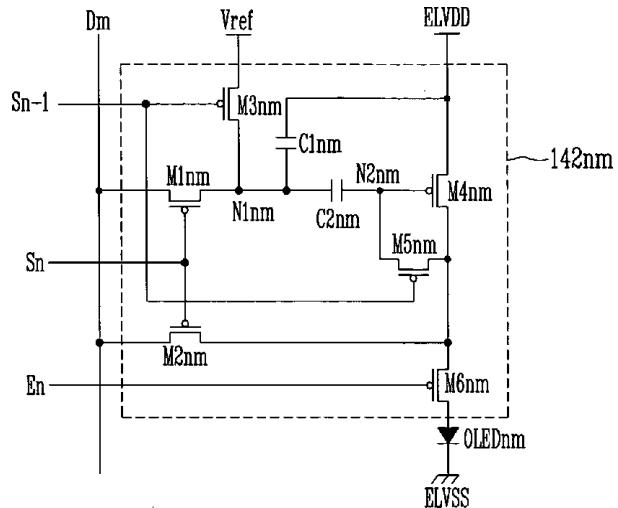

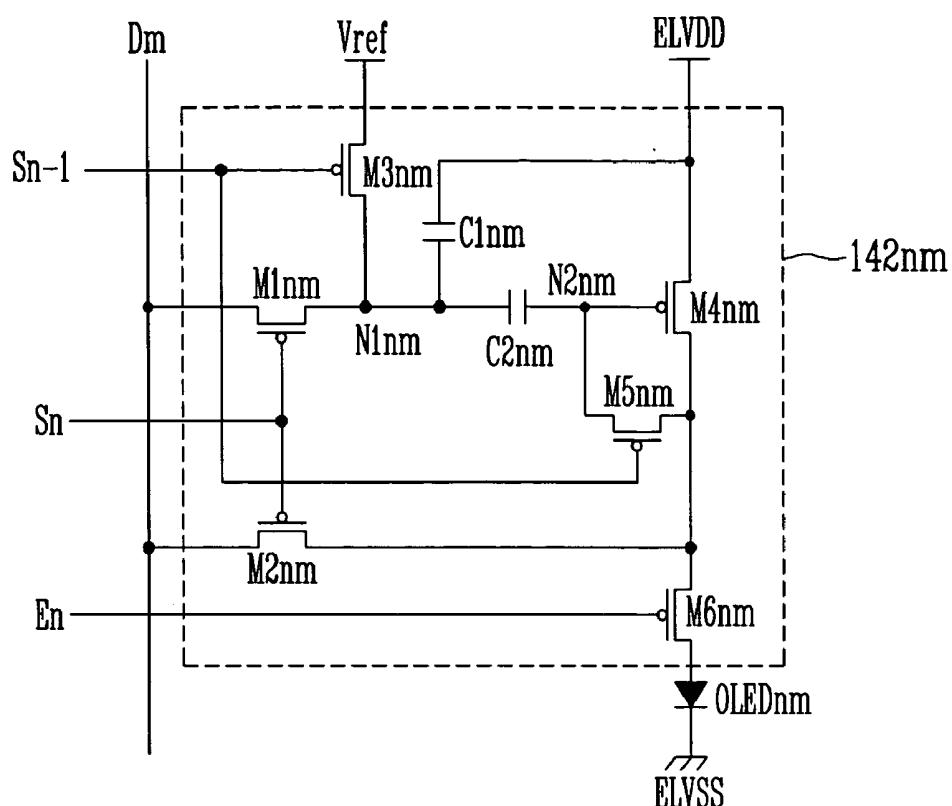

[0034] FIG. 3 illustrates a circuit diagram of an exemplary pixel employable in the light emitting display illustrated in FIG. 2;

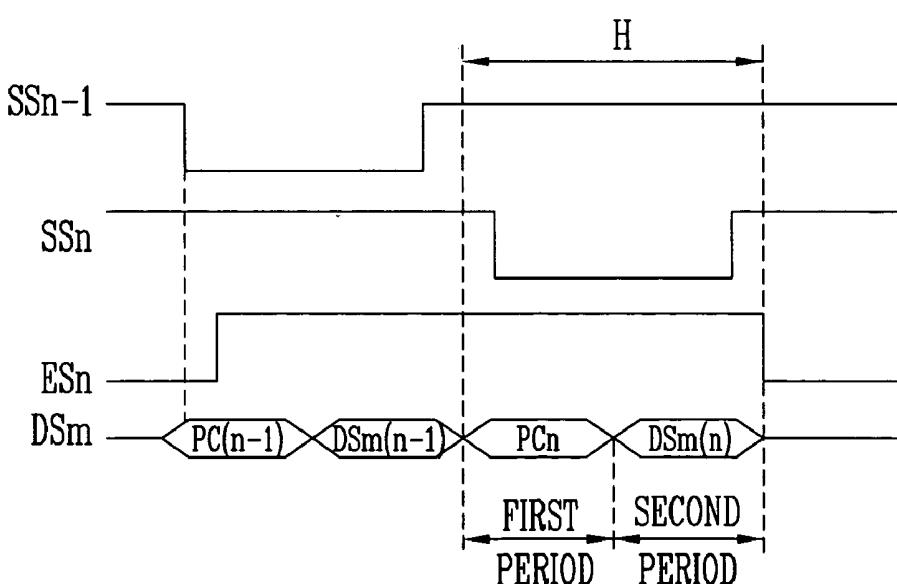

[0035] FIG. 4 illustrates exemplary waveforms employable for driving the pixel illustrated in FIG. 3;

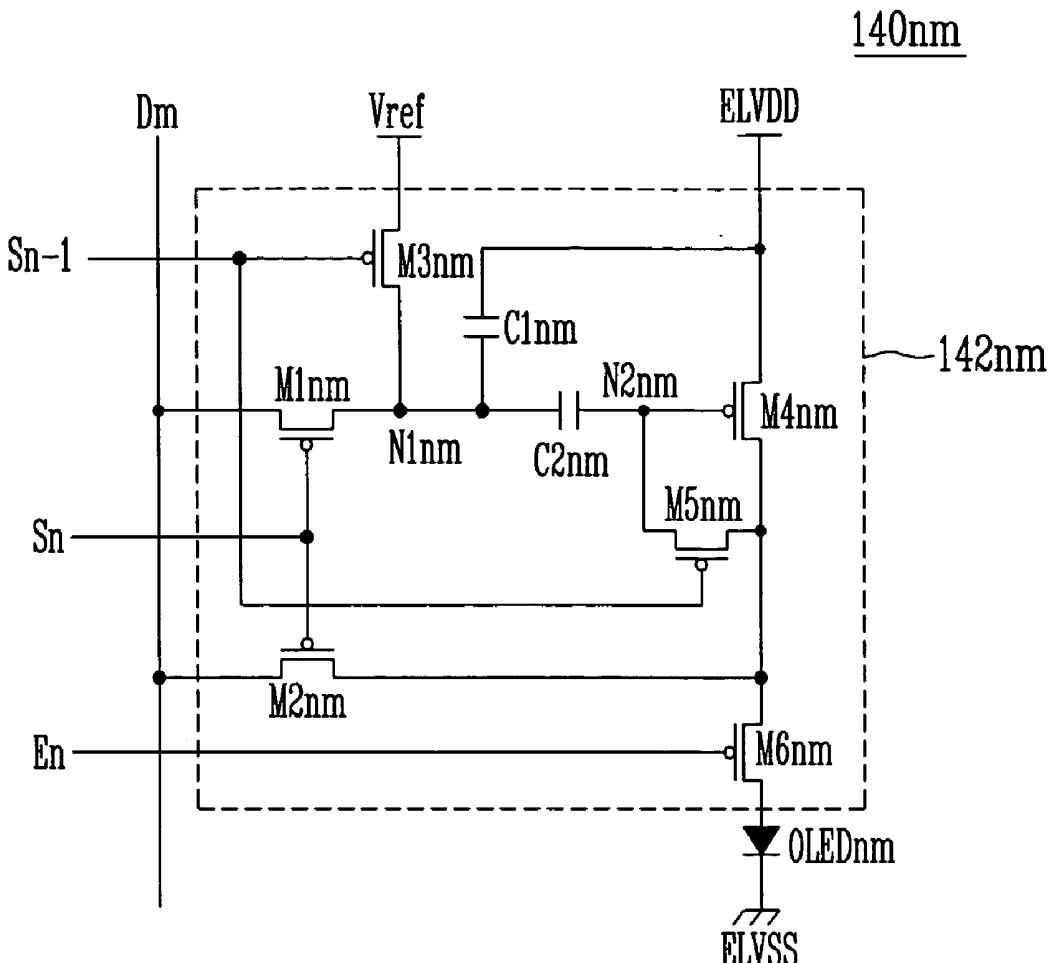

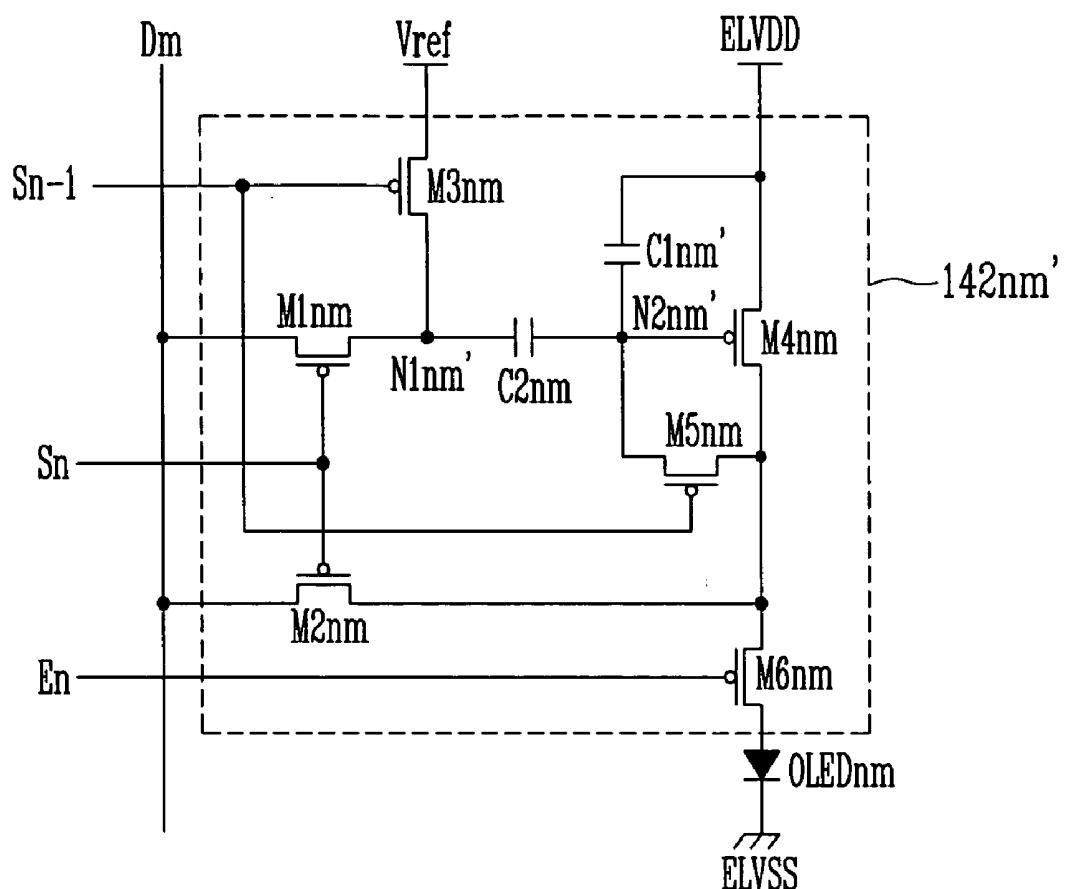

[0036] FIG. 5 illustrates a circuit diagram of another exemplary pixel employable in the light emitting display illustrated in FIG. 2;

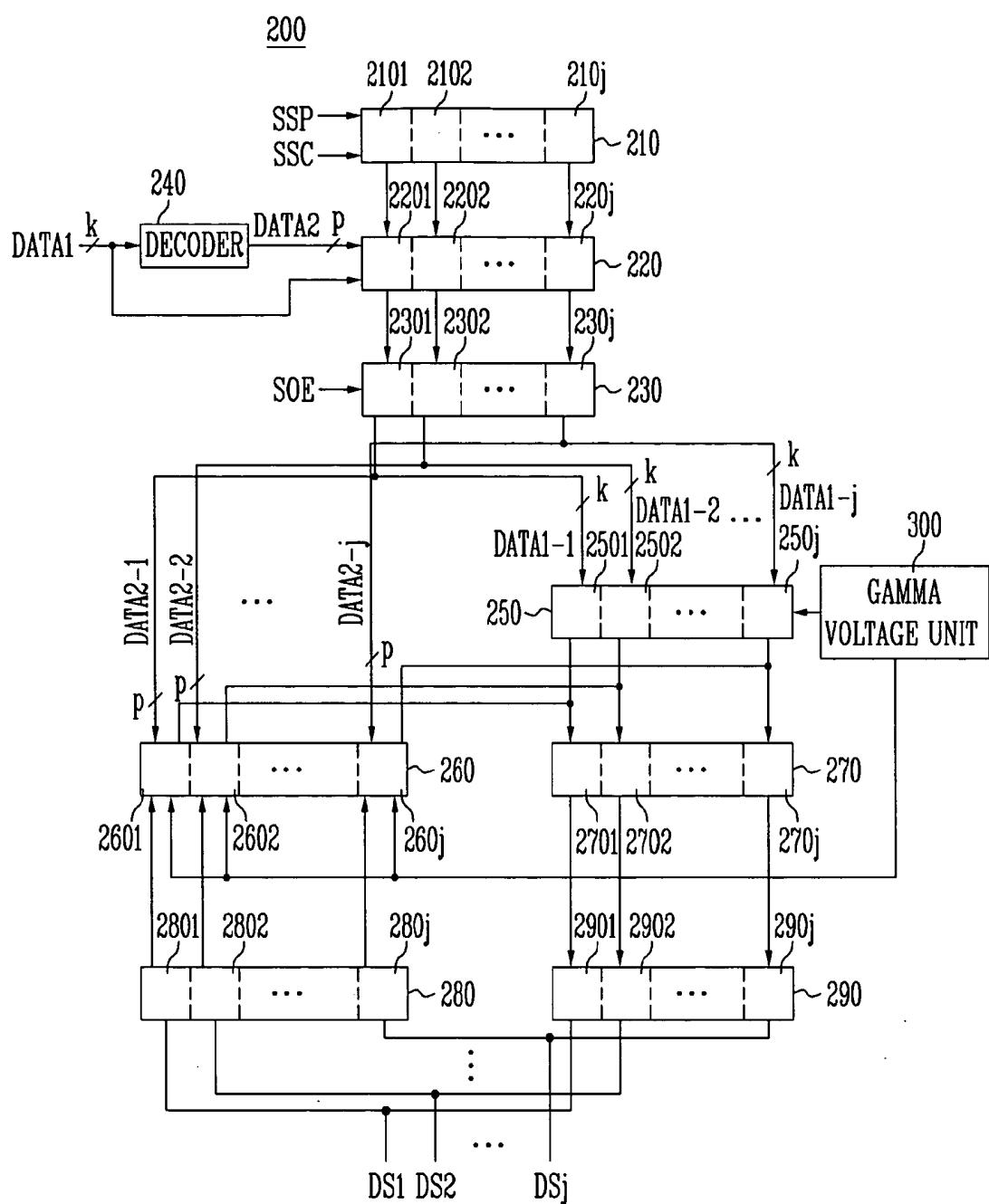

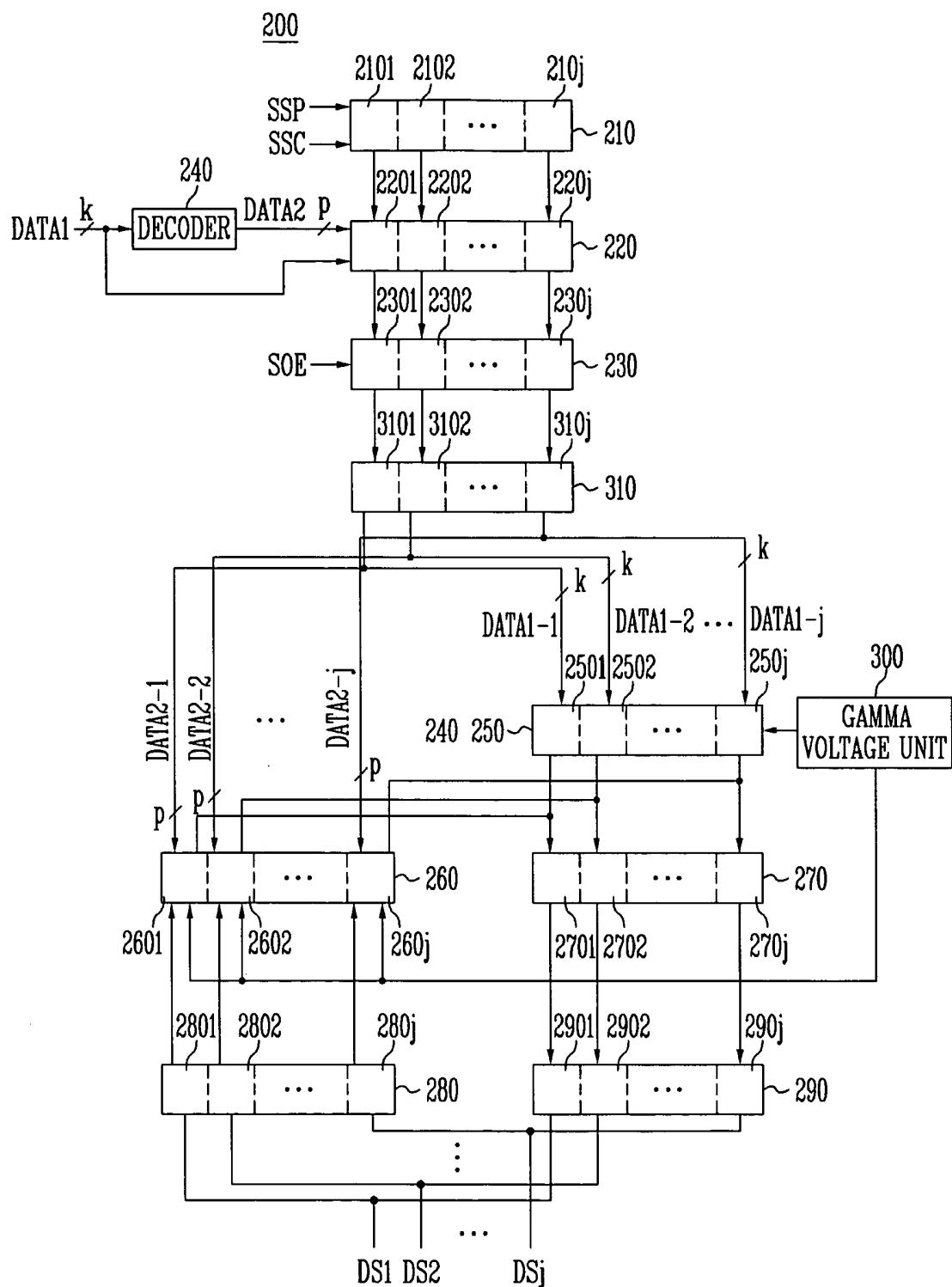

[0037] FIG. 6 is a block diagram illustrating a first embodiment of the data driving circuit illustrated in FIG. 2;

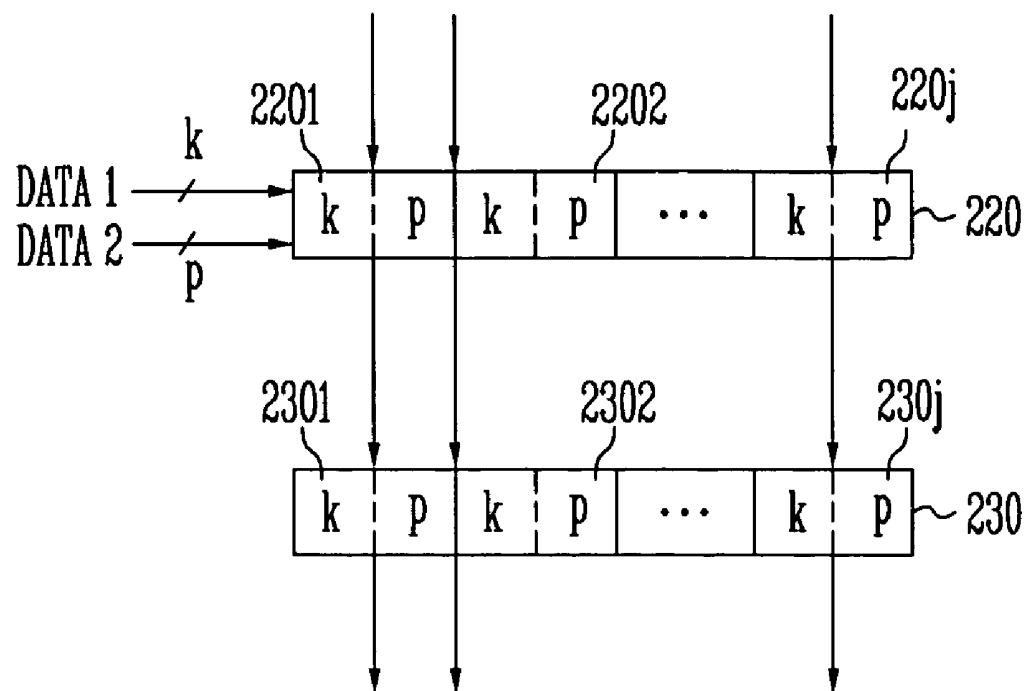

[0038] FIG. 7 illustrates an embodiment of the sampling latch unit and the holding latch unit illustrated in FIG. 6;

[0039] FIG. 8 illustrates a block diagram of a second embodiment of the data driving circuit illustrated in FIG. 2;

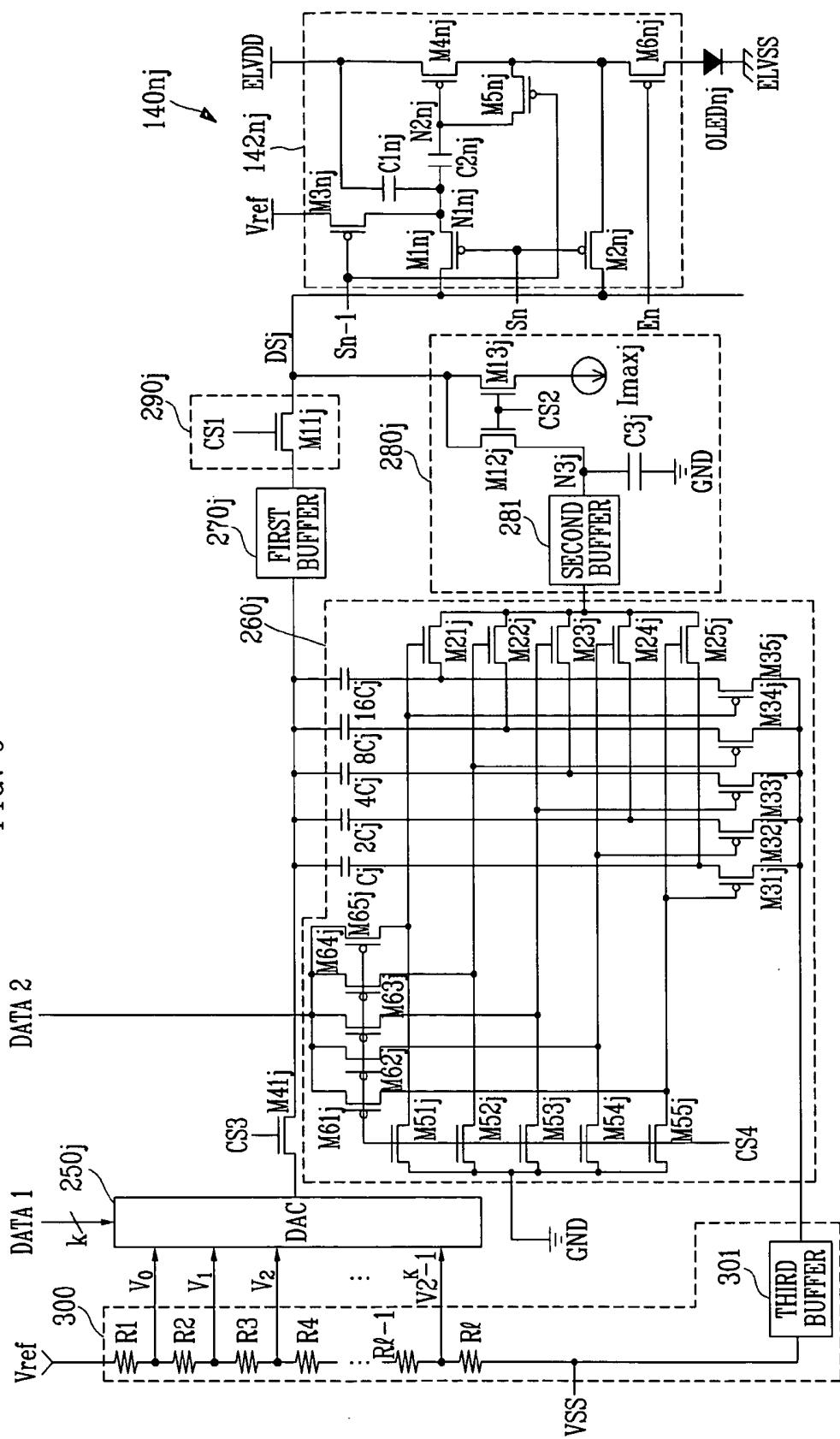

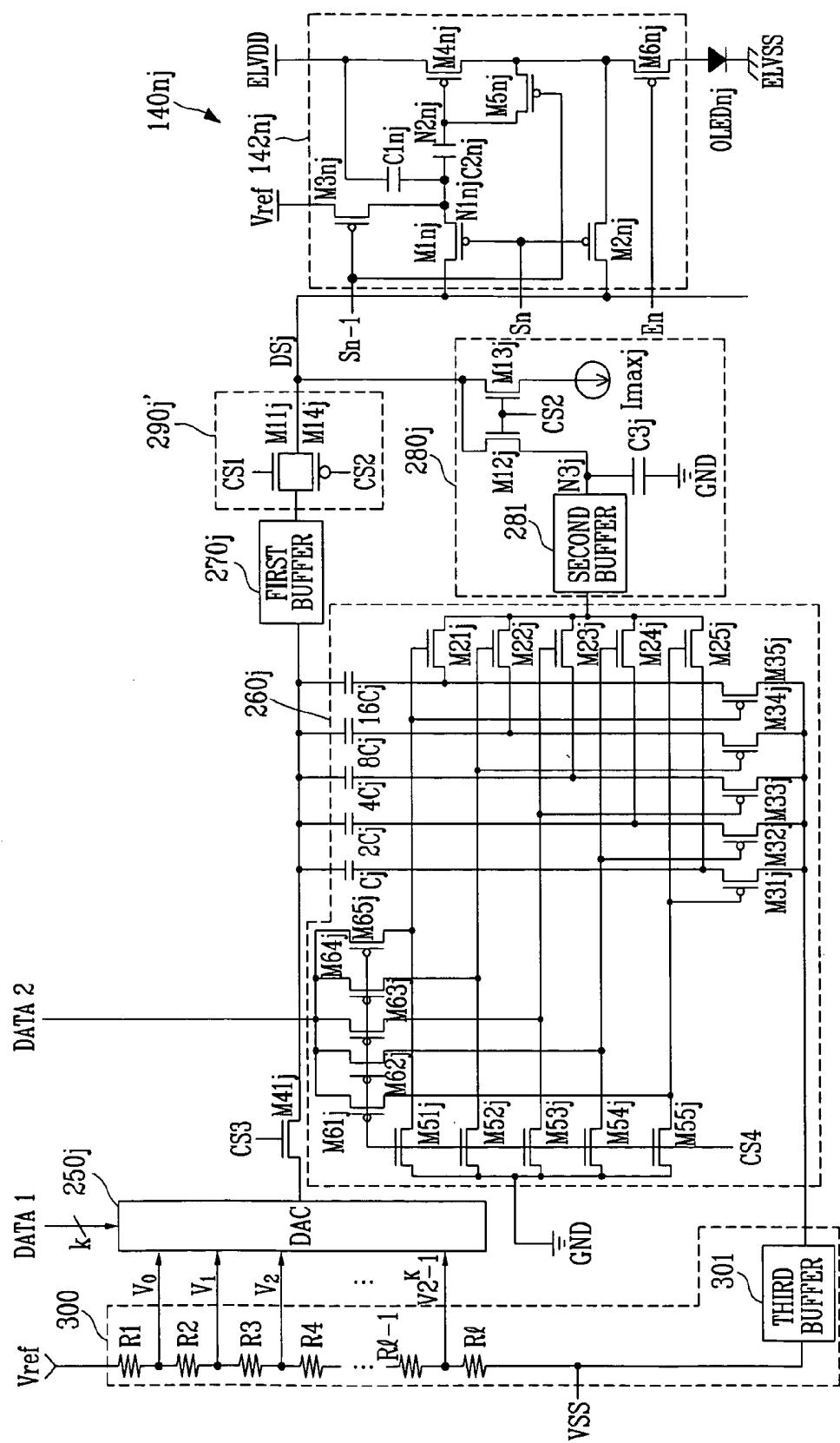

[0040] FIG. 9 illustrates a schematic diagram of a first embodiment of a connection scheme connecting a gamma voltage unit, a digital-to-analog converter unit, a switching unit, a voltage controlling unit and a current sink unit illustrated in FIG. 6, and a pixel illustrated in FIG. 3;

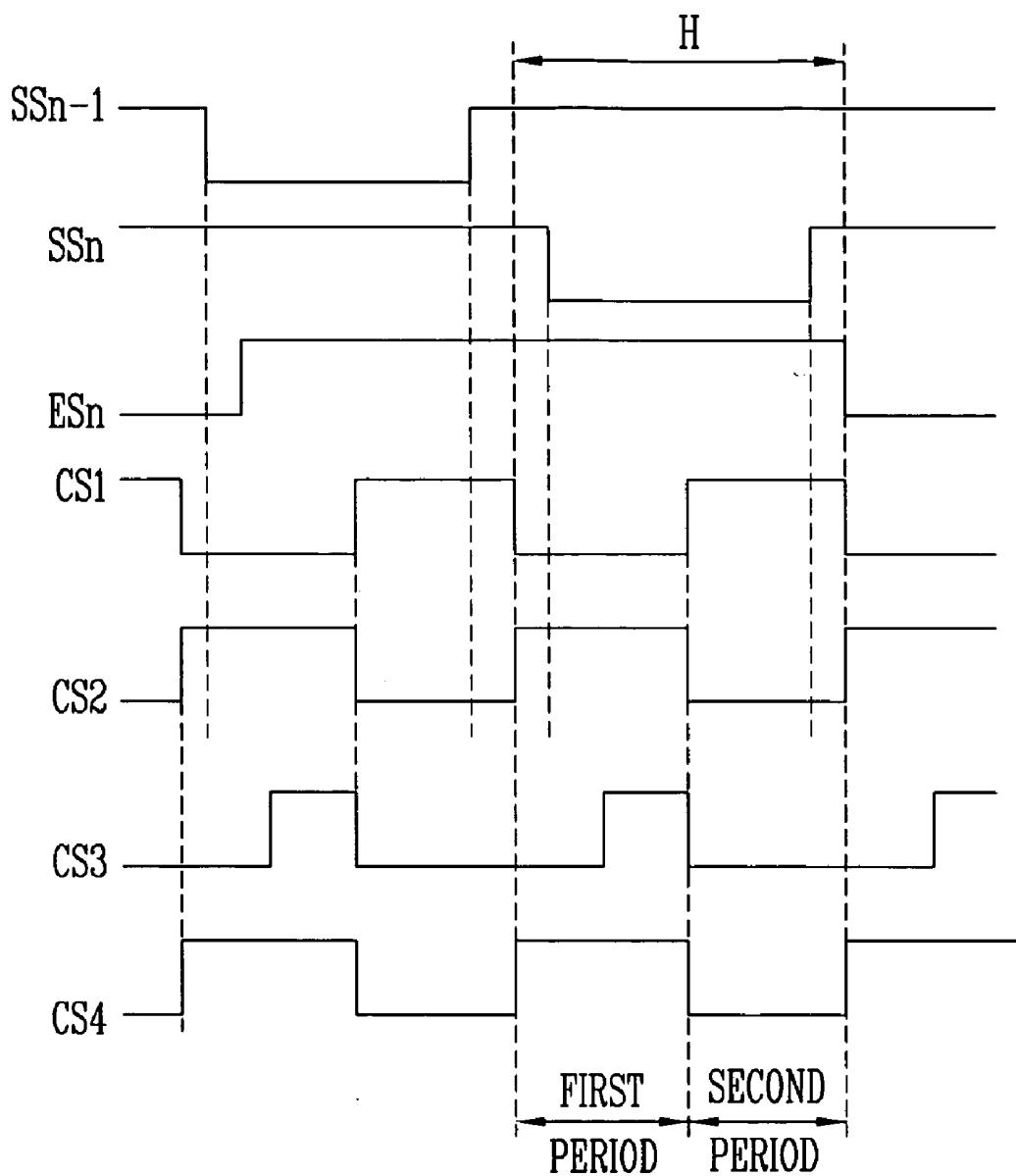

[0041] FIG. 10 illustrates exemplary waveforms employable for driving the pixel, the switching unit and the current sink illustrated in FIG. 9;

[0042] FIG. 11 illustrates the connection scheme illustrated in FIG. 9 employing another embodiment of a switching unit; and

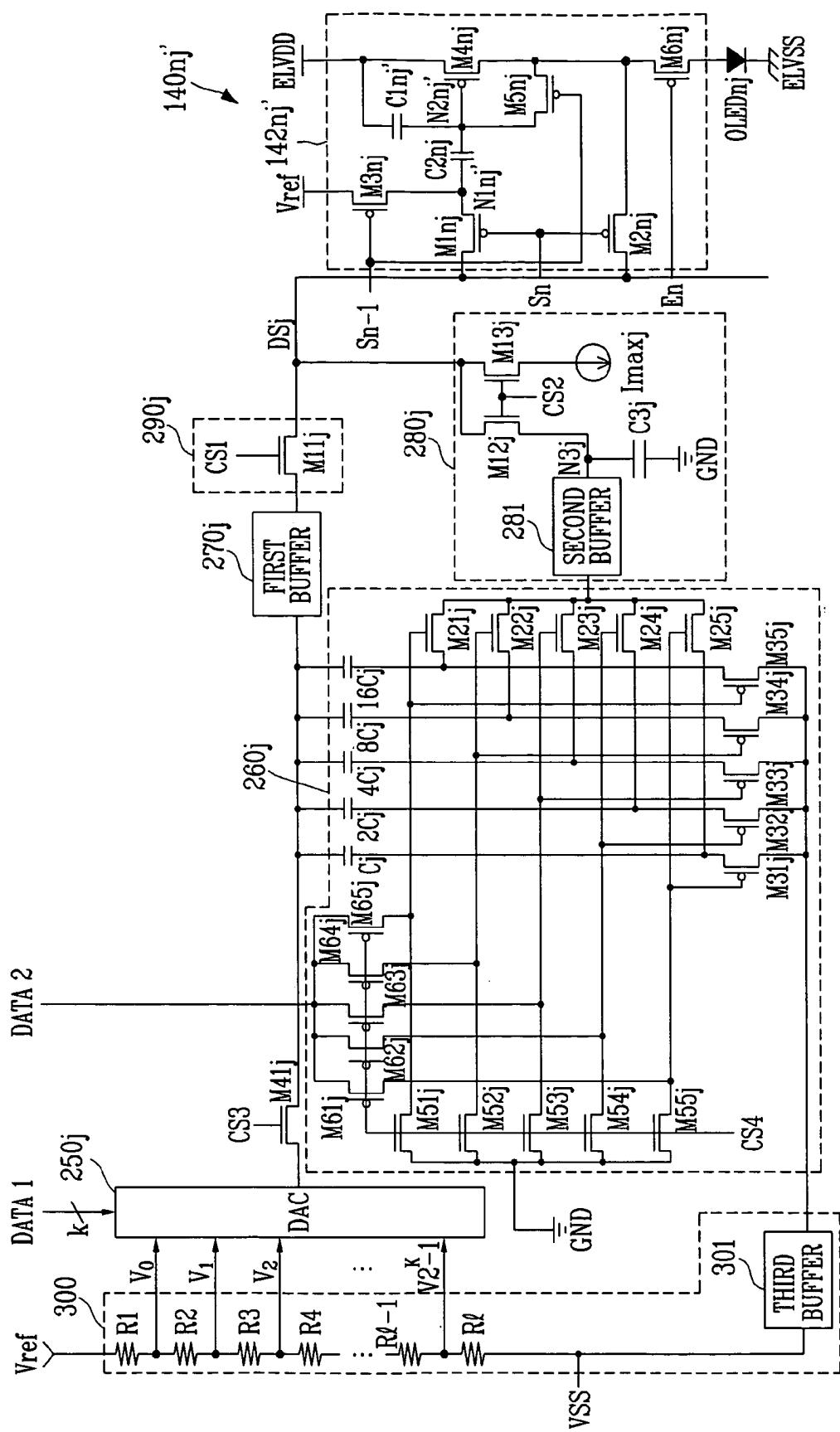

[0043] FIG. 12 illustrates a schematic diagram of a second embodiment of a connection scheme connecting a gamma voltage unit, a digital-to-analog converter unit, a switching unit, a voltage controlling unit and a current sink unit illustrated in FIG. 6, and a pixel illustrated in FIG. 5.

#### DETAILED DESCRIPTION OF THE INVENTION

[0044] Korean Patent Application No. 2005-0070439, filed on Aug. 1, 2005, in the Korean Intellectual Property Office, and entitled, "Data Driving Circuit and Organic Light Emitting Display Using the Same," is incorporated by reference herein in its entirety.

[0045] The present invention will now be described more fully hereinafter with reference to the accompanying drawings, in which exemplary embodiments of the invention are shown. The invention may, however, be embodied in different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the invention to those skilled in the art. Like reference numerals refer to like elements throughout.

[0046] Hereinafter, exemplary embodiments of the present invention will be described with reference to FIGS. 2 to 12. In data driving circuits and light emitting displays employing one or more aspects of the invention, because a voltage value of the data signal is reset using a compensation voltage generated when current sinks from a respective pixel, uniform images can be displayed regardless of electron mobility, threshold voltages, etc. of transistors.

[0047] FIG. 2 illustrates a schematic diagram of a light emitting display according to an embodiment of the present invention.

[0048] As shown in FIG. 2, the light emitting display may include a scan driver 110, a data driver 120, a pixel unit 130 and a timing controller 150. The pixel unit 130 may include a plurality of pixels 140. The pixel unit 130 may include n×m pixels 140 arranged, for example, in n rows and m columns, where n and m may each be integers. The pixels 140 may be connected to scan lines S1 to Sn, emission control lines E1 to En and data lines D1 to Dm. The pixels 140 may be respectively formed in the regions partitioned by the emission control lines E1 to En and the data lines D1 to Dm. The scan driver 110 may drive the scan lines S1 to Sn and the emission control lines E1 to En. The data driver 120 may drive the data lines D1 to Dm. The timing controller 150 may control the scan driver 110 and the data driver 120. The data driver 120 may include one or more data driving circuits 200.

[0049] The timing controller 150 may generate data driving control signals DCS and scan driving control signals SCS in response to externally supplied synchronizing signals (not shown). The data driving control signals DCS generated by the timing controller 150 may be supplied to the data driver 120. The scan driving control signals SCS generated by the timing controller 150 may be supplied to the scan driver 110. The timing controller 150 may supply first data DATA1 to the data driver 120 in accordance with the externally supplied data (not shown).

[0050] The scan driver 110 may receive the scan driving control signals SCS from the timing controller 150. The scan driver 110 may generate scan signals SS1 to SSn based on the received scan driving control signals SCS and may sequentially and respectively supply the scan signals SS1 to SSn to the scan lines S1 to Sn. The scan driver 110 may sequentially supply emission control signals ES1 to ESn to the emission control lines E1 to En. Each of the emission control signals ES1 to ESn may be supplied, e.g., changed from a low voltage signal to a high voltage signal, such that an "on" emission control signal, e.g., a high voltage signal, at least partially overlaps at least two of the scan signals SS1 to SSn. Therefore, in embodiments of the invention, a pulse width of the emission control signals ES1 to ESn may be equal to or larger than a pulse width of the scan signals SS1 to SSn.

[0051] The data driver 120 may receive the data driving control signals DCS from the timing controller 150. The data driver 120 may generate data signals DS1 to DSM based on the received data driving control signals DCS and the first data DATA1. The generated data signals DS1 to DSM may be supplied to the data lines D1 to Dm in synchronization with the scan signals SS1 to SSn supplied to the scan lines S1 to Sn. For example, when the first scan signal SS1 is supplied, the generated data signals DS1 to DSM corresponding to the pixels 140(1)(1 to m) may be synchronously supplied to the first to the m-th pixels in the first row via the data lines D1 to Dm, and when the nth scan signal SSn is supplied, the generated data signals DS1 to DSM corresponding to the pixels 140(n)(1 to m) may be synchronously supplied to the first to the m-th pixels in the n-th row via the data lines D1 to Dm.

[0052] The data driver 120 may supply predetermined currents to the data lines D1 to Dm during a first period of one horizontal period 1H for driving one or more of the pixels 140. For example, one horizontal period 1H may correspond to a complete period associated with one of the scan signals SS1 to SSn and a corresponding one of the data signals DS1 to DSM being supplied to the respective pixel 140 in order to drive the respective pixel 140. The data driver 120 may supply predetermined voltages to the data lines D1 to Dm during a second period of the one horizontal period 1H. For example, one horizontal period 1H may correspond to a complete period associated with one of the scan signals SS1 to SSn and a corresponding one of the data signals DS1 to DSM being supplied to the respective pixel 140 in order to drive the respective pixel 140. In embodiments of the invention, the data driver 120 may include at least one data driving circuit 200 for supplying such predetermined currents and predetermined voltages during the first and second periods of one horizontal period 1H. In the following description, the predetermined voltages that may be supplied to the data lines D1 to Dm during the second period will be referred to as the data signals DS1 to DSM.

[0053] The pixel unit 130 may be connected to a first power source ELVDD for supplying a first voltage VDD, a second power source ELVSS for supplying a second voltage VSS and a reference power source ELVref for supplying a reference voltage Vref to the pixels 140. The first power source ELVDD, the second power source ELVSS and the reference power source ELVref may be externally provided. The pixels 140 may receive the first voltage VDD signal and the second voltage VSS signal, and may control the currents that flow through respective light emitting devices/materials, e.g., OLEDs, in accordance with the data signals DS1 to DSM that may be supplied by the data driver 120 to the pixels 140. The pixels 140 may thereby generate light components corresponding to the received first data DATA1.

[0054] Some or all of the pixels 140 may receive the first voltage VDD signal, the second voltage VSS signal and the reference voltage Vref signal from the respective first, second and reference power sources ELVDD, ELVSS and ELVref. The pixels 140 may compensate for a voltage drop in the first voltage VDD signal and/or threshold voltage(s) using the reference voltage Vref signal. The amount of compensation may be based on a difference between voltage values of the reference voltage Vref signal and the first voltage VDD signal respectively supplied by the reference power source ELVref and the first power source ELVDD.

The pixels **140** may supply respective currents from the first power source ELVDD to the second power source ELVSS via, e.g., the OLEDs in response to the respective data signals DS<sub>1</sub> to DS<sub>m</sub>. In embodiments of the invention, each of the pixels **140** may have, for example, the structure illustrated in FIG. 3 or FIG. 5.

[0055] FIG. 3 illustrates a circuit diagram of an nm-th exemplary pixel **140nm** employable in the light emitting display illustrated in FIG. 2. For simplicity, FIG. 3 illustrates the nm-th pixel that may be the pixel provided at the intersection of the n-th row of scan lines S<sub>n</sub> and the m-th row of data lines D<sub>m</sub>. The nm-th pixel **140nm** may be connected to the m-th data line D<sub>m</sub>, the n-1th and nth scan lines S<sub>n-1</sub> and S<sub>n</sub> and the nth emission control line E<sub>n</sub>. For simplicity, FIG. 3 only illustrates one exemplary pixel **140nm**. In embodiments of the invention, the structure of the exemplary pixel **140nm** may be employed for all or some of the pixels **140** of the light emitting display.

[0056] Referring to FIG. 3, the nm-th pixel **140nm** may include a light emitting material/device, e.g., OLED<sub>nm</sub>, and an nm-th pixel circuit **142nm** for supplying current to the associated light emitting material/device.

[0057] The nm-th OLED<sub>nm</sub> may generate light of a pre-determined color in response to the current supplied from the nm-th pixel circuit **142nm**. The nm-th OLED<sub>nm</sub> may be formed of, e.g., organic material, phosphor material and/or inorganic material.

[0058] In embodiments of the invention, the nm-th pixel circuit **142nm** may generate a compensation voltage for compensating for variations within and/or among the pixels **140** such that the pixels **140** may display images with uniform brightness. The nm-th pixel circuit **142nm** may generate the compensation voltage using a previously supplied scan signal of the scan signals SS<sub>1</sub> to SS<sub>n</sub> during each scan cycle. In embodiments of the invention, one scan cycle may correspond to scan signals SS<sub>1</sub> to SS<sub>n</sub> being sequentially supplied. Thus, in embodiments of the invention, during each cycle, the n-1th scan signal SS<sub>n-1</sub> may be supplied prior to the nth scan signal SS<sub>n</sub> and when the n-1th scan signal SS<sub>n-1</sub> is being supplied to the n-1th scan line of the light emitting display, the nm-th pixel circuit **142nm** may employ the n-1th scan signal SS<sub>n-1</sub> to generate a compensation voltage. For example, the second pixel in the second column, i.e., the pixel **140<sub>22</sub>**, may generate a compensation voltage using the first scan signal SS<sub>1</sub>.

[0059] The compensation voltage may compensate for a voltage drop in a source voltage signal and/or a voltage drop resulting from a threshold voltage of the transistor of the nm-th pixel circuit **142nm**. For example, the nm-th pixel circuit **142nm** may compensate for a voltage drop of the first voltage VDD signal and/or a threshold voltage of a transistor, e.g., a threshold voltage of a fourth transistor M<sub>4nm</sub> of the pixel circuit **142nm** based on the compensation voltage that may be generated using a previously supplied scan line during the same scan cycle.

[0060] In embodiments of the invention, the pixel circuit **142nm** may compensate for a drop in the voltage of the first power source ELVDD and the threshold voltage of the fourth transistor M<sub>4nm</sub> when the n-1th scan signal SS<sub>n-1</sub> is supplied to the n-1th scan line S<sub>n-1</sub>, and may charge the voltage corresponding to the data signal DS<sub>m</sub> when the nth

scan signal SS<sub>n</sub> is supplied to the nth scan line S<sub>n</sub>. In embodiments of the invention, the pixel circuit **142nm** may include first to sixth transistors M<sub>1nm</sub> to M<sub>6nm</sub>, a first capacitor C<sub>1nm</sub> and a second capacitor C<sub>2nm</sub> to generate the compensation voltage and to drive the light emitting material/device.

[0061] A first electrode of the first transistor M<sub>1nm</sub> may be connected to the data line D<sub>m</sub> and a second electrode of the first transistor M<sub>1nm</sub> may be connected to a first node N<sub>1nm</sub>. A gate electrode of the first transistor M<sub>1nm</sub> may be connected to the nth scan line S<sub>n</sub>. The first transistor M<sub>1nm</sub> may be turned on when the nth scan signal SS<sub>n</sub> is supplied to the nth scan line S<sub>n</sub>. When the first transistor M<sub>1nm</sub> is turned on, the data line D<sub>m</sub> may be electrically connected to the first node N<sub>1nm</sub>.

[0062] A first electrode of the first capacitor C<sub>1nm</sub> may be connected to the first node N<sub>1nm</sub> and a second electrode of the first capacitor C<sub>1nm</sub> may be connected to the first power source ELVDD.

[0063] A first electrode of the second transistor M<sub>2nm</sub> may be connected to the data line D<sub>m</sub> and a second electrode of the second transistor M<sub>2nm</sub> may be connected to a second electrode of the fourth transistor M<sub>4nm</sub>. A gate electrode of a second transistor M<sub>2nm</sub> may be connected to the nth scan line S<sub>n</sub>. The second transistor M<sub>2nm</sub> may be turned on when the nth scan signal SS<sub>n</sub> is supplied to the nth scan line S<sub>n</sub>. When the second transistor M<sub>2nm</sub> is turned on, the data line D<sub>m</sub> may be electrically connected to the second electrode of the fourth transistor M<sub>4nm</sub>.

[0064] A first electrode of the third transistor M<sub>3nm</sub> may be connected to the reference power source ELVref and a second electrode of the third transistor M<sub>3nm</sub> may be connected to the first node N<sub>1nm</sub>. A gate electrode of the third transistor M<sub>3nm</sub> may be connected to the n-1th scan line S<sub>n-1</sub>. The third transistor M<sub>3nm</sub> may be turned on when the n-1th scan signal SS<sub>n-1</sub> is supplied to the n-1th scan line S<sub>n-1</sub>. When the third transistor M<sub>3nm</sub> is turned on, the reference voltage Vref may be electrically connected to the first node N<sub>1nm</sub>.

[0065] A first electrode of the fourth transistor M<sub>4nm</sub> may be connected to the first power source ELVDD and the second electrode of the fourth transistor M<sub>4nm</sub> may be connected to a first electrode of the sixth transistor M<sub>6nm</sub>. A gate electrode of the fourth transistor M<sub>4nm</sub> may be connected to the second node N<sub>2nm</sub>.

[0066] A first electrode of the second capacitor C<sub>2nm</sub> may be connected to the first node N<sub>1nm</sub> and a second electrode of the second capacitor C<sub>2nm</sub> may be connected to the second node N<sub>2nm</sub>.

[0067] In embodiments of the invention, the first and second capacitors C<sub>1nm</sub> and C<sub>2nm</sub> may be charged when the n-1th scan signal SS<sub>n-1</sub> is supplied. In particular, the first and second capacitors C<sub>1nm</sub> and C<sub>2nm</sub> may be charged and the fourth transistor M<sub>4nm</sub> may supply a current corresponding to a voltage at the second node N<sub>2nm</sub> to the first electrode of the sixth transistor M<sub>6nm</sub>.

[0068] A second electrode of the fifth transistor M<sub>5nm</sub> may be connected to the second node N<sub>2nm</sub> and a first electrode of the fifth transistor M<sub>5nm</sub> may be connected to the second electrode of the fourth transistor M<sub>4nm</sub>. A gate

electrode of the fifth transistor M<sub>5nm</sub> may be connected to the n-1th scan line S<sub>n-1</sub>. The fifth transistor M<sub>5nm</sub> may be turned on when the n-1th scan signal S<sub>Sn-1</sub> is supplied to the n-1th scan line S<sub>n-1</sub> so that current flows through the fourth transistor M<sub>4nm</sub>. Therefore, the fourth transistor M<sub>4nm</sub> may operate as a diode.

[0069] The first electrode of the sixth transistor M<sub>6nm</sub> may be connected to the second electrode of the fourth transistor M<sub>4nm</sub> and a second electrode of the sixth transistor M<sub>6nm</sub> may be connected to an anode electrode of the nm-th OLED<sub>nm</sub>. A gate electrode of the sixth transistor M<sub>6nm</sub> may be connected to the nth emission control line E<sub>n</sub>. The sixth transistor M<sub>6nm</sub> may be turned off when an emission control signal E<sub>Sn</sub>, e.g., a high voltage signal, is supplied to the nth emission control line E<sub>n</sub> and may be turned on when no emission control signal, e.g., a low voltage signal, is supplied to the nth emission control line E<sub>n</sub>.

[0070] In embodiments of the invention, the emission control signal E<sub>Sn</sub> supplied to the nth emission control line E<sub>n</sub> may be supplied to at least partially overlap both the n-1th scan signal S<sub>Sn-1</sub> that may be supplied to the n-1th scan line S<sub>n-1</sub> and the nth scan signal S<sub>Sn</sub> that may be supplied to nth scan line S<sub>n</sub>. Therefore, the sixth transistor M<sub>6nm</sub> may be turned off when the n-1th scan signal S<sub>Sn-1</sub>, e.g., a low voltage signal is supplied to the n-1th scan line S<sub>n-1</sub> and the nth scan signal S<sub>Sn</sub>, e.g., a low voltage signal, is supplied to the nth scan line S<sub>n</sub> so that a predetermined voltage may be charged in the first and second capacitors C<sub>1nm</sub> and C<sub>2nm</sub>. The sixth transistor M<sub>6nm</sub> may be turned on during other times to electrically connect the fourth transistor M<sub>4nm</sub> and the nm-th OLED<sub>nm</sub> to each other. In the exemplary embodiment shown in FIG. 3, the transistors M<sub>1nm</sub> to M<sub>6nm</sub> are PMOS transistors, which may turn on when a low voltage signal is supplied to the respective gate electrode and may turn on when a high voltage signal is supplied to the respective gate electrode. However, the present invention is not limited to PMOS devices.

[0071] In the pixel illustrated in FIG. 3, because the reference power source ELVref does not supply current to the pixels 140, a drop in the voltage of the reference voltage Vref may not occur. Therefore, it is possible to maintain the voltage value of the reference voltage Vref signal uniform regardless of the positions of the pixels 140. In embodiments of the invention, the voltage value of the reference voltage Vref may be equal to or different from the first voltage ELVDD.

[0072] FIG. 4 illustrates exemplary waveforms that may be employed for driving the exemplary nm-th pixel 140nm illustrated in FIG. 3. As shown in FIG. 4, each horizontal period 1H for driving the nm-th pixel 140nm may be divided into a first period and a second period. During the first period, predetermined currents (PCs) may respectively flow through the data lines D<sub>1</sub> to D<sub>m</sub>. During the second period, the data signals DS<sub>1</sub> to DS<sub>m</sub> may be supplied to the respective pixels 140 via the data lines D<sub>1</sub> to D<sub>m</sub>. During the first period, the respective PCs may be supplied from each of the pixel(s) 140 to a data driving circuit 200 that may be capable of functioning, at least in part, as a current sink. During the second period, the data signals DS<sub>1</sub> to DS<sub>m</sub> may be supplied from the data driving circuit 200 to the pixel(s)

140. For simplicity, in the following description, it will be assumed that, at least initially, i.e., prior to any voltage drop that may result during operation of the pixels 140, the voltage value of the reference voltage Vref signal is equal to the voltage value of the first voltage VDD signal.

[0073] Exemplary methods of operating the nm-th pixel circuit 142nm of the nm-th pixel 140nm of the pixels 140 will be described in detail with reference to FIGS. 3 and 4. First, the n-1th scan signal S<sub>Sn-1</sub> may be supplied to the n-1th scan line S<sub>n-1</sub> to control the on/off operation of the m pixels that may be connected to the n-1th scan line S<sub>n-1</sub>. When the scan signal S<sub>Sn-1</sub> is supplied to the n-1th scan line S<sub>n-1</sub>, the third and fifth-transistors M<sub>3nm</sub> and M<sub>5nm</sub> of the nm-th pixel circuit 142nm of the nm pixel 140nm may be turned on. When the fifth transistor M<sub>5nm</sub> is turned on, current may flow through the fourth transistor M<sub>4nm</sub> so that the fourth transistor M<sub>4nm</sub> may operate as a diode. When the fourth transistor M<sub>4nm</sub> operates as a diode, the voltage value of the second node N<sub>2nm</sub> may correspond to a difference between the threshold voltage of the fourth transistor M<sub>4nm</sub> and the voltage of the first voltage VDD signal being supplied by the first power source ELVDD.

[0074] More particularly, when the third transistor M<sub>3nm</sub> is turned on, the reference voltage Vref signal from the reference power source ELVref may be applied to the first node N<sub>1nm</sub>. The second capacitor C<sub>2nm</sub> may be charged with a voltage corresponding to the difference between the first node N<sub>1nm</sub> and the second node N<sub>2nm</sub>. In embodiments of the invention in which the reference voltage Vref signal from the reference power source ELVref and the first voltage VDD from the first power source ELVDD may, at least initially, i.e., prior to any voltage drop that may result during operation of the pixels 140, be equal, the voltage corresponding to the threshold voltage of the fourth transistor M<sub>4nm</sub> may be charged in the second capacitor C<sub>2nm</sub>. In embodiments of the invention in which a predetermined drop in voltage of the first voltage VDD signal occurs, the threshold voltage of the fourth transistor M<sub>4nm</sub> and a voltage corresponding to the magnitude of the voltage drop of the first power source ELVDD may be charged in the second capacitor C<sub>2nm</sub>.

[0075] In embodiments of the invention, during the period where the n-1th scan signal S<sub>Sn-1</sub> may be supplied to the n-1th scan line S<sub>n-1</sub>, a predetermined voltage corresponding to the sum of the voltage corresponding to the voltage drop of the first voltage VDD signal and the threshold voltage of the fourth transistor M<sub>4nm</sub> may be charged in the second capacitor C<sub>2nm</sub>. By storing the voltage corresponding to a sum of the voltage drop of the first voltage VDD signal from the first power source ELVDD and the threshold voltage of the fourth transistor M<sub>4nm</sub> during operation of the respective n-1 pixel of in the m-th column, it is possible to later utilize the stored voltage to compensate for both the voltage drop of the first voltage VDD signal and the threshold voltage during operation of the respective nm-th pixel 140nm.

[0076] In embodiments of the invention, the voltage corresponding to the sum of the threshold voltage of the fourth transistor M<sub>4nm</sub> and the difference between the reference voltage signal Vref and the first voltage VDD signal may be charged in the second capacitor C<sub>2nm</sub> before the nth scan signal S<sub>Sn</sub> is supplied to the nth scan line S<sub>n</sub>. When the nth

scan signal SS<sub>n</sub> is supplied to the nth scan line S<sub>n</sub>, the first and second transistors M<sub>1nm</sub> and M<sub>2nm</sub> may be turned on. During the first period of one horizontal period, when the second transistor M<sub>2nm</sub> of the pixel circuit 142nm of the nm-th pixel 140nm is turned on, the PC may be supplied from the nm-th pixel 140nm to the data driving circuit 200 via the data line D<sub>m</sub>. In embodiments of the invention, the PC may be supplied to the data driving circuit 200 via the first power source ELVDD, the fourth transistor M<sub>4nm</sub>, the second transistor M<sub>2nm</sub> and the data line D<sub>m</sub>. A predetermined voltage may then be charged in the first and second capacitors C<sub>1nm</sub> and C<sub>2nm</sub> in response to the supplied PC.

[0077] The data driving circuit 200 may reset a voltage of a gamma voltage unit (not shown) based on a predetermined voltage value, i.e., compensation voltage that may be generated when the PC sinks, as described above. The reset voltage from the gamma voltage unit (not shown) may be used to generate the data signals DS<sub>1</sub> to DS<sub>m</sub> to be respectively supplied to the data lines D<sub>1</sub> to D<sub>m</sub>.

[0078] In embodiments of the invention, the generated data signals DS<sub>1</sub> to DS<sub>m</sub> may be respectively supplied to the respective data lines D<sub>1</sub> to D<sub>m</sub> during the second period of the one horizontal period. More particularly, e.g., the respective generated data signal DS<sub>m</sub> may be supplied to the respective first node N<sub>1nm</sub> via the first transistor M<sub>1nm</sub> during the second period of the one horizontal period. Then, the voltage corresponding to difference between the data signal DS<sub>m</sub> and the first power source ELVDD may be charged in the first capacitor C<sub>1nm</sub>. The second node N<sub>2nm</sub> may then float and the second capacitor C<sub>2nm</sub> may maintain the previously charged voltage.

[0079] In embodiments of the invention, during the period when the n-1 pixel in the m-th column is being controlled and the scan signal SS<sub>n-1</sub> is being supplied to the previous scan line S<sub>n-1</sub>, a voltage corresponding to the threshold voltage of the fourth transistor M<sub>4nm</sub> and the voltage drop of the first voltage VDD signal from the first power source ELVDD may be charged in the second capacitor C<sub>2nm</sub> of the nm-th pixel 140nm to compensate for the voltage drop of the first voltage VDD signal from the first power source ELVDD and the threshold voltage of the fourth transistor M<sub>4nm</sub>.

[0080] In embodiments of the invention, during the period when the n-th scan signal SS<sub>n</sub> is supplied to the n-th scan line S<sub>n</sub>, the voltage of the gamma voltage unit (not shown) may be reset so that the electron mobility of the transistors included in the respective n-th pixels 140n associated with each data line D<sub>1</sub> to D<sub>m</sub> may be compensated for and the respective generated data signals DS<sub>1</sub> to DS<sub>m</sub> may be supplied to the n-th pixels 140n using the respective reset gamma voltages. Therefore, in embodiments of the invention, non-uniformity in the threshold voltages of the transistors and the electron mobility may be compensated, and images with uniform brightness may be displayed. Processes for resetting the voltage of the gamma voltage unit will be described below.

[0081] FIG. 5 illustrates another exemplary embodiment of an nm-th pixel 140nm' employable by the light emitting display illustrated in FIG. 2. The structure of the nm-th pixel 140nm' illustrated in FIG. 5 is substantially the same as the structure of the nm-th pixel 140nm illustrated in FIG. 3, but for the arrangement of a first capacitor C<sub>1nm'</sub> in a pixel circuit 142nm' and respective connections to a first node

N<sub>1nm'</sub> and a second node N<sub>2nm'</sub>. In the exemplary embodiment illustrated in FIG. 5, a first electrode of the first capacitor C<sub>1nm'</sub> may be connected to the second node N<sub>2nm'</sub> and a second electrode of the first capacitor C<sub>1nm'</sub> may be connected to the first power source ELVDD. A first electrode of the second capacitor C<sub>2nm</sub> may be connected to the first node N<sub>1nm'</sub> and a second electrode of the second capacitor C<sub>2nm</sub> may be connected to the second node N<sub>2nm'</sub>. The first node N<sub>1nm'</sub> may be connected to the second electrode of the first transistor M<sub>1nm</sub>, the second electrode of the third transistor M<sub>3nm</sub> and the first electrode of the second capacitor C<sub>2nm</sub>. The second node N<sub>2nm'</sub> may be connected to the gate electrode of the fourth transistor M<sub>4nm</sub>, the second electrode of the fifth transistor M<sub>5nm</sub>, the first electrode of the first capacitor C<sub>1nm'</sub> and the second electrode of the second capacitor C<sub>2nm</sub>.

[0082] In the following description, the same reference numerals employed above in the description of the nm-th pixel 140nm shown in FIG. 3 will be employed to describe like features in the exemplary embodiment of the nm-th pixel 140nm' illustrated in FIG. 5.

[0083] Exemplary methods for operating the nm-th pixel circuit 142nm' of the nm-th pixel 140nm' of the pixels 140 will be described in detail with reference to FIGS. 4 and 5. First, during a horizontal period for driving the n-1 pixels 140(n-1)(1 to m), i.e., the pixels arranged in the (n-1)th row, when the n-1th scan signal SS<sub>n-1</sub> is supplied to the n-1th scan line S<sub>n-1</sub>, the third and fifth transistors M<sub>3nm</sub> and M<sub>5nm</sub> of the n-th pixel(s) 140(n)(1 to m), i.e., the pixels arranged in the n-th row, may be turned on.

[0084] When the fifth transistor M<sub>5nm</sub> is turned on, current may flow through the fourth transistor M<sub>4nm</sub> so that the fourth transistor M<sub>4nm</sub> may operate as a diode. When the fourth transistor M<sub>4nm</sub> operates as a diode, a voltage corresponding to a value obtained by subtracting the threshold voltage of the fourth transistor M<sub>4nm</sub> from the first power source ELVDD may be applied to a second node N<sub>2nm'</sub>. The voltage corresponding to the threshold voltage of the fourth transistor M<sub>4nm</sub> may be charged in the first capacitor C<sub>1nm'</sub>. As shown in FIG. 5, the first capacitor C<sub>1nm'</sub> may be provided between the second node N<sub>2nm'</sub> and the first power source ELVDD.

[0085] When the third transistor M<sub>3nm</sub> is turned on, the voltage of the reference power source ELVref may be applied to the first node N<sub>1nm'</sub>. Then, the second capacitor C<sub>2nm</sub> may be charged with the voltage corresponding to difference between a first node N<sub>1nm'</sub> and the second node N<sub>2nm'</sub>. During the period where the n-1th scan signal SS<sub>n-1</sub> is supplied to the n-1th scan line S<sub>n-1</sub> and the first and second transistors M<sub>1nm</sub> and M<sub>2nm</sub> may be turned off, the data signal DS<sub>m</sub> may not be supplied to the nm-th pixel 140nm'.

[0086] Then, during the first period of the one horizontal period 1H for driving the nm-th pixel 140nm', the scan signal SS<sub>n</sub> may be supplied to the nth scan line S<sub>n</sub> and the first and second transistors M<sub>1nm</sub> and M<sub>2nm</sub> may be turned on. When the second transistor M<sub>2nm</sub> is turned on, during the first period of the one horizontal period, the respective PC may be supplied from the nm-th pixel 140nm' to the data driving circuit 200 via the data line D<sub>m</sub>. The PC may be supplied to the data driving circuit 200 via the first power source ELVDD, the fourth transistor M<sub>4nm</sub>, the second

transistor M<sub>2nm</sub> and the data line D<sub>m</sub>. In response to the PC, predetermined voltage may be charged in the first and second capacitors C<sub>1nm'</sub> and C<sub>2nm</sub>.

[0087] The data driving circuit 200 may reset the voltage of the gamma voltage unit using the compensation voltage applied in response to the PC to generate the data signal DS using the respectively reset voltage of the gamma voltage unit.

[0088] Then, during the second period of the one horizontal period for driving the nm-th pixel 140nm', the data signal DS<sub>m</sub> may be supplied to the first node N<sub>1nm'</sub>. The predetermined voltage corresponding to the data signal DS<sub>m</sub> may be charged in the first and second capacitors C<sub>1nm'</sub> and C<sub>2nm</sub>.

[0089] When the data signal DS<sub>m</sub> is supplied, the voltage of the first node N<sub>1nm'</sub> may fall from the voltage Vref of the reference power source ELVref to the voltage of the data signal DS<sub>m</sub>. At this time, as the second node N<sub>2nm'</sub> may be floating, the voltage value of the second node N<sub>2nm'</sub> may be reduced in response to the amount of voltage drop of the first node N<sub>1nm'</sub>. The amount of reduction in voltage that may occur at the second node N<sub>2nm'</sub> may be determined by the capacitances of the first and second capacitors C<sub>1nm'</sub> and C<sub>2nm</sub>.

[0090] When the voltage of the second node N<sub>2nm'</sub> falls, the predetermined voltage corresponding to the voltage value of the second node N<sub>2nm'</sub> may be charged in the first capacitor C<sub>1nm'</sub>. When the voltage value of the reference power source ELVref is fixed, the amount of voltage charged in the first capacitor C<sub>1nm'</sub> may be determined by the data signal DS<sub>m</sub>. That is, in the nm-th pixel 140nm' illustrated in FIG. 5, because the voltage values charged in the capacitors C<sub>1nm'</sub> and C<sub>2nm</sub> may be determined by the reference power source ELVref and the data signal DS<sub>m</sub>, it may be possible to charge a desired voltage irrespective of the voltage drop of the first power source ELVDD.

[0091] In embodiments of the invention, the voltage of the gamma voltage unit may be reset so that the electron mobility of the transistors included in each of the pixels 140 may be compensated for and the respective generated data signal may be supplied using the reset gamma voltage. In embodiments of the invention, non-uniformity among the threshold voltages of the transistors and deviation in the electron mobility of the transistors may be compensated for, thereby enabling images with uniform brightness to be displayed.

[0092] FIG. 6 illustrates a block diagram of a first exemplary embodiment of the data driving circuit illustrated in FIG. 2. For simplicity, in FIG. 6, it is assumed that the data driving circuit 200 has j channels, where j is a natural number equal to or greater than 2.

[0093] As shown in FIG. 6, the data driving circuit 200 may include a shift register unit 210, a sampling latch unit 220, a holding latch unit 230, a decoder unit 240, a digital-analog converter unit (hereinafter, referred to as a DAC) 250, a voltage controller unit 260, a first buffer unit 270, a current supply unit 280, a selector 290 and a gamma voltage unit 300.

[0094] The shift register unit 210 may receive a source shift clock SSC and a source start pulse SSP from the timing

controller 150. The shift register unit 210 may utilize the source shift clock SSC and the source start pulse SSP to sequentially generate j sampling signals while shifting the source start pulse SSP every one period of the source shift clock SSC. The shift register unit 210 may include j shift registers 2101 to 210j.

[0095] The decoder unit 240 may include j decoders 2401 through 240j. Each of the decoders 2401 through 240j may receive k bits of the respective first data DATA1 and may convert the k bits of the first data DATA1 into p (p is a natural number) bits of second data DATA2. In embodiments of the invention, each of the decoders 2401 through 240j may generate p bits of second data DATA2 using a binary weighted value.

[0096] In embodiments of the invention, the weighted value of the externally received first data DATA1 may be determined to allow the gamma voltage unit 300 to be set a predetermined voltage. For example, the number of bits of the first data DATA1 allowing a desired gray scale voltage to be selected from a plurality of gray scale voltages may be determined. The plurality of gray scale voltages may be generated by the gamma voltage unit 300. The decoders 2401 through 240j may convert k bits of the first data DATA1, corresponding to the gray scale voltages, into respective p bits of second data DATA2-1 to DATA2-j using a binary weighted value. For example, the decoders 2401 through 240j may generate five bits of the second data DATA2 using eight bits of the first data DATA1.

[0097] In embodiments of the invention, at least one decoder 240 may be provided. The decoder 240 may be connected to the sampling latch unit 220, as shown in FIG. 6. In such embodiments, when the first data DATA1 are sequentially supplied from the timing controller 150, the decoder 240 may receive the first data DATA1 and supply, e.g., the k-bits of first data DATA1 and p-bits of second data DATA2, resulting from the conversion, to the sampling latch unit 220. In embodiments of the invention, when the first data DATA1 corresponding to, e.g., red, green, and blue, are simultaneously input from the timing controller 150, three decoders 240 may be provided and the decoders 240 may be connected to the sampling latch unit 220.

[0098] The sampling latch unit 220 may sequentially store the respective first data DATA1 and the second data DATA2 in response to sampling signals sequentially supplied from the shift register unit 210. The sampling latch unit 220 may include j sampling latches 2201 to 220j in order to respectively store the j first data DATA1-1 to DATA1-j and the j second data DATA2-1 to DATA2-j. Each of the sampling latches 2201 to 220j may have a magnitude corresponding to a total number of bits of the first data DATA1 and the second data DATA2. For example, as shown in FIG. 7, in embodiments of the invention in which the first data DATA1 has k bits and the second data has p bits, each of the sampling latches 2201 to 220j may have a magnitude of (k+p) bits such that the sampling latches 2201 to 220j may respectively store (k+p)-bits of each of the j first data DATA1-1 to DATA1-j and the j second data DATA2-1 to DATA2-j.

[0099] The holding latch unit 230 may receive the first data DATA1 and the second data DATA2 from the sampling latch unit 220 to store the first data DATA1 and the second data DATA2 when a source output enable SOE signal is input to the holding latch unit 230. The holding latch unit

**230** may supply the first data DATA1 and/or the second data DATA2 stored therein to the DAC unit **250** and/or the voltage controlling unit **260** when the SOE signal is input. The holding latch unit **230** may include j holding latches **2301** to **230j** in order to store the j first data DATA1-1 to DATA1-j and the j second data DATA2-1 to DATA2-j. Each of the holding latches **2301** to **230j** may have a magnitude corresponding to a total number of bits of the first data DATA1 and the second data DATA2. For example, as shown in FIG. 7, each of the holding latches **2301** to **230j** may have a magnitude of (k+p) bits so that the k bits of each of the j first data DATA1-1 to DATA1-j and the p bits of each of the j second data DATA2-1 to DATA2-j may be respectively stored.

[0100] The current supply unit **280** may sink the predetermined current PC from the respective pixel(s) **140** selected by one of the scan signals SS1 to SS<sub>n</sub>. The current supply unit **280** may receive the sinking current via the respective one of the data lines D1 through Dj, during the first period of each horizontal period.

[0101] In embodiments of the invention, the current supply unit **280** may sink an amount of current corresponding to a minimum amount of current that may be employed by the respective light emitter, e.g., OLED, to emit light of maximum brightness. Then, the current supply unit **280** may supply a predetermined compensation voltage to the voltage controller unit **260**. The compensation voltage may be generated while the respective predetermined current PC was sinking. In the exemplary embodiment illustrated in FIG. 6, the current supply unit **280** includes j current sink units **2801** through **280j**.

[0102] The gamma voltage unit **300** may generate predetermined gray scale voltages corresponding to the k bits of the first data DATA1. The gamma voltage unit **300**, as shown in FIG. 8, may include a plurality of distribution or voltage dividing resistors R1 through R/ and may generate  $2^k$  gray scale voltages. The gray scale voltages generated by the gamma voltage unit **300** may be supplied to the DAC unit **250**.

[0103] The DAC unit **250** may include j DACs **2501** through **250j**. The gray scale voltages generated by the gamma voltage unit **300** may be supplied to each of the j DACs **2501** through **250j**. Each of the DACs **2501** through **250j** may select, as a data signal DS, one of the gray scale voltages that may be supplied by the gamma voltage unit **300** based on the respective first data DATA1-1 to DATA1-j supplied from the respective holding latch units **2301** through **230j**. For example, the DACs **2501** to **250j** may respectively select, as a data signal DS, one of the gray scale voltages that may be supplied by the gamma voltage unit **300** based on a number of bits of the respective first data DATA1-1 to DATA1-j.

[0104] The voltage controller unit **260** may include j voltage controllers **2601** through **260j**.

[0105] The voltage controllers **2601** through **260j** may each receive a compensation voltage, e.g., voltage supplied via the respective current sink unit **2801-280j** or the second data DATA2, and a third supply voltage signal VSS'. In embodiments of the invention, a same power source or a different power source may be employed for supplying the second voltage VSS signal and the third supply voltage VSS'

signal. The third supply voltage VSS' signal may be supplied to a terminal of the gamma voltage unit **300**. The voltage controllers **2601** through **260j**, which may receive the compensation voltage and/or the second data DATA2, and the third supply voltage VSS' signal, may control a voltage value of the selected data signal DS so that variations among the pixels **140**, such as, variations due to electron mobility, threshold voltage, etc. of transistors included in the respective pixels **140** may be compensated for.

[0106] The first buffer unit **270** may supply the respective data signal DS to the selector **290**. As discussed above, the voltage of the respective data signal may be controlled by the voltage control unit **260**. In embodiments of the invention, the first buffer unit **270** may include j first buffers **2701** through **270j**.

[0107] The selector **290** may control electrical connections between the data lines D1 to Dj and the first buffers **2701** to **270j**. The selector **290** may electrically connect the data lines D1 to Dj and the first buffers **2701** to **270j** to each other during the second period of the one horizontal period 1H. In embodiments of the invention, the selector **290** may electrically connect the data lines D1 to Dj and the first buffers **2701** to **270j** to each other only during the second period. During periods other than the second period, the selector **290** may keep the data lines D1 to Dj and the first buffers **2701** to **270j** electrically disconnected from each other.

[0108] The selector **290** may include j switching units **2901** to **290j**. The generated respective data signals DS1 to DS<sub>j</sub> may be respectively supplied from the first buffers **2701** to **270j** to the data lines D1 to Dj via the switching units **2901** to **290j**. In embodiments of the invention, the selection unit **290** may employ other types of switching units. FIG. 11 illustrates another exemplary embodiment of a switching unit switching unit **290j** that may be employed by the selector **290**.

[0109] As shown in FIG. 8, in a second exemplary embodiment, the data driving circuit **200** may include a level shifter **310** that is connected to the holding latch unit **230**. The level shifter **310** may include level registers **3101** to **310j** and may raise the voltage levels of the first data DATA1 and the second data DATA2 supplied from the holding latch unit **230** and may supply the first data DATA1 and the second data DATA2 to the DAC unit **250** and the voltage controller **260**. When the data (not shown) being supplied from an external system to the data driving circuit **200** has high voltage levels, circuit components with high voltage resistant properties should generally be provided, thus, increasing the manufacturing cost. In embodiments of the invention, the data being supplied from an external system to the data driving circuit **200** may have low voltage levels and the low voltage level may be transitioned to a high voltage level by the level shifter **310**. In embodiments of the invention the first data DATA1 may correspond to the externally supplied data.

[0110] FIG. 9 illustrates a first embodiment of a connection scheme for connecting the gamma voltage unit **300**, the DAC **250j**, the voltage controller **260j**, the switching unit **290j** and the current sink unit **280j** shown in FIG. 6 and a pixel **140nj**. For simplicity, FIG. 9 only illustrates one channel, i.e., the jth channel, and it is assumed that the data

line Dj is connected to an nj-th pixel **140nj** according to the exemplary embodiment of the pixel **140nm** illustrated in FIG. 3.

[0111] As shown in FIG. 9, the gamma voltage unit **300** may include a plurality of distribution resistors R1 to R/. The distribution resistors R1 to R/ may be disposed between the reference supply voltage Vref and the third supply voltage VSS'. The distribution resistors R1 to R/ may distribute or divide a voltage supplied thereto. For example, the distribution resistors R1 to R/ may distribute or divide a voltage between the reference supply voltage Vref and the third supply voltage VSS', and may generate a plurality of gray scale voltages V0 through V $2^k$ -1. The distribution resistors R1 to R/ may supply the generated gray scale voltages V0 through V $2^k$ -1 to the DAC **250j**. The gamma voltage unit **300** may supply the third supply voltage VSS' to the voltage controller **260j** via a third buffer **301**.

[0112] The DAC unit **250** may include j DACs **2501** through **250j**. The gray scale voltages generated by the gamma voltage unit **300** may be supplied to each of the j DACs **2501** through **250j**. Each of the DACs **2501** through **250j** may select, as a data signal DS, one of the gray scale voltages V0 to V $2^k$ -1 that may be supplied by the gamma voltage unit **300** based on the respective first data DATA1. The DAC **250j** may select one of the gray scale voltages V0 to V $2^k$ -1, as the data signal DS, based on a bit value of the first data DATA1-1 to DATA1-j. The DAC **250j** may supply the selected gray scale voltage to the first buffer **270j**.

[0113] The DAC **250j** may select one gray scale voltage among the gray scale voltages V0 to V $2^k$ -1 in response to the bit values of the first data Data1 as the data signal DS to supply the data signal DS to the first buffer **270j**. A forty-first transistor M41j may be provided between the DAC **250j** and the first buffer **270j**. A first electrode of the forty-first transistor M41j may be connected to the DAC **250j**. A second electrode of the forty-first transistor M41j may be connected to the first buffer **270j**. The forty-first transistor M41j may be controlled by a third control signal CS3 supplied to a gate electrode of the forty-first transistor M41j, as illustrated in FIGS. 9 and 10. As shown in FIG. 10, the forty-first transistor M41j may be turned on during a portion of the first period of one horizontal period to supply the data signal DS supplied from the DAC **250j** to the first buffer **270j** via the forty-first transistor M41j. As shown in FIG. 10, a voltage of the third control signal CS3 may change, e.g., rise, after a voltage of the second control signal CS2 changes, e.g., rises, and may change again, e.g., fall, at a same time as the voltage of the second control signal CS2 changes again, e.g., falls.

[0114] The current sink unit **280j** may include a twelfth transistor M12j and a thirteenth transistor M13j, a current source Imaxj, a third capacitor C3j, a third node N3j, a ground voltage source GND and a second buffer **281**. The twelfth transistor M12j and the thirteenth transistor M13j may be controlled by the second control signal CS2. The current source Imaxj may be connected to a first electrode of the thirteenth transistor M13j. The third capacitor C3j may be connected between the third node N3j and the ground voltage source GND. The second buffer **281j** may be connected between the third node N3j and the voltage controller **260j**.

[0115] A gate electrode of the twelfth transistor M12j may be connected to a gate electrode of the thirteenth transistor

M13j. A second electrode of the twelfth transistor M12j may be connected to a second electrode of the thirteenth transistor M13j and the data line Dj. A first electrode of the twelfth transistor M12j may be connected to the second buffer **281**. The twelfth transistor M12j and the thirteenth transistor M13j may be turned on during the first period of each horizontal period 1H. The twelfth transistor M12j and the thirteenth transistor M13j may be turned off during the second period of the horizontal period 1H. The second control signal CS2 may control the on/off state of the twelfth transistor M12j and the thirteenth transistor M13j.

[0116] During the first period of one horizontal period 1H, the current source Imaxj may receive, from the pixel **140nj**, at least a minimum amount of current that may be supplied to the light emitter, e.g., OLEDnj, for the pixel **140nj** to emit light with maximum brightness. As discussed above, the second control signal CS2 may control the twelfth transistor M12j and the thirteenth transistor M13j to be on during the first period 1H, thereby allowing the predetermined current PC to flow from the pixel **140nj** to the current sink unit **280j**. When the twelfth transistor M12j and the thirteenth transistor M13j are on during the first period of one horizontal period, the current source Imaxj of the current sink unit **280j** may receive an amount of current corresponding to a minimum amount of current that may be supplied to the OLEDnj for the pixel **140nj** to emit light with maximum brightness. The respective light emitting device, e.g., OLEDnj, may emit light of maximum brightness when at least a voltage corresponding to a highest one of the plurality of gray scale voltages V0 to V $2^k$ -1 is supplied to the light emitting device.

[0117] The third capacitor C3j may store a compensation voltage that may be applied to the third node N3j when the current from the pixel **140nj** sinks to the current source Imaxj. The third capacitor C3j may store the compensation voltage applied to the third node N3j during the first period of one horizontal period 1H, and may maintain the compensation voltage at the third node N3j stable even when the twelfth transistor M13 and the thirteenth transistor M13 are turned off.

[0118] The second buffer **281j** may transfer the compensation voltage applied to the third node N3j to the voltage controller **260j**.

[0119] The voltage controller **260j** may receive the compensation voltage, the second data Data2 and/or the voltage of the third supply voltage VSS' to control the voltage value of the data signal DSj. In the description of exemplary embodiments, reference term "p" will be equal to five, however, "p" may be any positive integer.

[0120] To control the voltage value of the data signal DSj, the voltage controller **260j** may include p capacitors Cj, 2Cj, 4Cj, 8Cj and 16Cj, a first set of p PMOS transistors M31j, M32j, M33j, M34j and M35j and a first set of p NMOS transistors M21j, M22j, M23j, M24j and M25j. The capacitors Cj, 2Cj, 4Cj, 8Cj and 16Cj may be connected to an electrical path connecting the forty-first transistor M41 and the first buffer **270j**. First electrodes of the first set of p PMOS transistors M31j, M32j, M33j, M34j and M35j may be connected to the third buffer **301** and second electrodes of the first set of p PMOS transistors M31j to M35j may be respectively connected to the first electrodes of the p capacitors Cj, 2Cj, 4Cj, 8Cj and 16Cj, respectively. Second elec-

trodes of the p capacitors C<sub>j</sub>, 2C<sub>j</sub>, 4C<sub>j</sub>, 8C<sub>j</sub> and 16C<sub>j</sub> may be connected to a second electrode of the forty-first transistor M<sub>41j</sub> and the first buffer 270<sub>j</sub>. First electrodes of the first set of p NMOS transistors M<sub>21j</sub>, M<sub>22j</sub>, M<sub>23j</sub>, M<sub>24j</sub> and M<sub>25j</sub> may be connected to the second buffer 281<sub>j</sub> and second electrodes of the first set of p NMOS transistors M<sub>21j</sub> to M<sub>25j</sub> may be respectively connected to the first electrodes of the p capacitors C<sub>j</sub>, 2C<sub>j</sub>, 4C<sub>j</sub>, 8C<sub>j</sub> and 16C<sub>j</sub>. Gate electrodes of the first set of p NMOS transistors M<sub>21j</sub> to M<sub>25j</sub> may be respectively connected to gate electrodes of the first set of p PMOS transistors M<sub>31j</sub> to M<sub>35j</sub>.

[0121] Capacitance values of the p capacitors C<sub>j</sub>, 2C<sub>j</sub>, 4C<sub>j</sub>, 8C<sub>j</sub> and 16C<sub>j</sub> may be relative to each other such that the capacitances of the p capacitors may increase along the order of 2<sup>0</sup>, 2<sup>1</sup>, 2<sup>2</sup>, 2<sup>3</sup> and 2<sup>4</sup>, respectively. For example, the capacitances of the p capacitors C<sub>j</sub>, 2C<sub>j</sub>, 4C<sub>j</sub>, 8C<sub>j</sub> and 16C<sub>j</sub> may have respective binary weighted values in accordance with the second data DATA2.

[0122] As shown in FIG. 9, the voltage controller 260<sub>j</sub> may include a second set of, e.g., p NMOS transistors M<sub>51j</sub>, M<sub>52j</sub>, M<sub>53j</sub>, M<sub>54j</sub> and M<sub>55j</sub> and a second set of, e.g., p PMOS transistors M<sub>61j</sub>, M<sub>62j</sub>, M<sub>63j</sub>, M<sub>64j</sub> and M<sub>65j</sub>. First electrodes of the second set of p NMOS transistors M<sub>51j</sub> to M<sub>55j</sub> may be connected to the ground voltage source GND. First electrodes of the second set of p PMOS transistors M<sub>61j</sub> to M<sub>65j</sub> may be connected to, e.g., the holding latch unit 230<sub>j</sub> or the level shifter 310<sub>j</sub> and may receive the second data DATA2. Second electrodes of the second set of p NMOS transistors M<sub>51j</sub>, M<sub>52j</sub>, M<sub>53j</sub>, M<sub>54j</sub> and M<sub>55j</sub> may be respectively connected to the gate electrodes of the first set of p PMOS transistors M<sub>31j</sub> to M<sub>35j</sub> and the gate electrodes of the first set of p NMOS transistors M<sub>21j</sub> to M<sub>25j</sub>. Gate electrodes of the second set of p NMOS transistors M<sub>51j</sub> to M<sub>55j</sub> may be respectively connected to gate electrodes of the second set of p PMOS transistors M<sub>61j</sub> to M<sub>65j</sub>.

[0123] As illustrated in FIG. 10, a fourth control signal CS4 may control the second set of p NMOS transistors M<sub>51j</sub> to M<sub>55j</sub>. The fourth control signal CS4 may turn on the second set of p NMOS transistors M<sub>51j</sub> to M<sub>55j</sub> during the first period of one horizontal period 1H and may turn off the second set of p NMOS transistors M<sub>51j</sub> to M<sub>55j</sub> during the second period of the horizontal period.

[0124] The second set of p NMOS transistors M<sub>51j</sub> to M<sub>55j</sub> may be turned on during the first period by the fourth control signal CS4. When the second set of p NMOS transistors are turned on, voltage from the ground voltage source GND may be supplied to the gate electrodes of the first set of p PMOS transistors M<sub>31j</sub> to M<sub>35j</sub>. Thus, the first set of p PMOS transistors M<sub>31j</sub> to M<sub>35j</sub> may be turned on during the first period of one horizontal period 1H. When the first set of p PMOS transistors M<sub>31j</sub> to M<sub>35j</sub> are turned on, voltage from the third supply voltage VSS' may be supplied via the third buffer 301 to the first electrodes of each of the fourth capacitors C, 2C, 4C, 8C, and 16C.

[0125] In embodiments of the invention, the first set of p PMOS transistors are formed of PMOS transistors and the second set of p NMOS transistors are formed of NMOS transistors, however, embodiments of the invention are not limited to such devices. In embodiments of the invention, a conduction type, e.g., P-type or N-type, of the first set of p PMOS transistors may be opposite from a conduction type of the second set of p NMOS transistors.

[0126] The second set of p PMOS transistors M<sub>61j</sub> to M<sub>65j</sub> may supply the second data DATA2 to the gate electrodes of the first set of p PMOS transistors M<sub>31j</sub> to M<sub>35j</sub> and the gate electrodes of the first set of p NMOS transistors M<sub>21j</sub> to M<sub>25j</sub>. In embodiments of the invention, the sixty-first transistor M<sub>61j</sub> of the second set of p PMOS transistors may receive a bit having a lowermost weight value in the second data DATA2 to supply the lowermost weight value bit to the twenty-fifth transistor M<sub>25j</sub> of the first set of p NMOS transistors. Depending on a value of the bit having the lowermost weight value, the twenty-fifth transistor M<sub>25j</sub> may be turned on or off. In embodiments of the invention, the twenty-fifth transistor M<sub>25j</sub> of the first set of p NMOS transistors may be turned on when the bit having the lowermost weight value is 1 and may be turned off when the bit having the lowermost weight value is 0.